# **BAT32G157 User Manual**

#### Ultra-low power 32-bit microcontroller based on ARM® Cortex®-M0+

Rev.1.0.5

Please note the following CMS IP policy

\* China Micro Semicon (Shenzhen) Co., Ltd. (hereinafter referred to as the Company) has applied for a patent and enjoys absolute legal rights and interests. The patent rights related to the Company's MCUs or other products have not been authorized to be licensed, and any company, organization or individual who infringes the Company's patent rights through improper means will take all possible legal actions to curb the infringer's improper infringement and recover the losses suffered by the Company as a result of the infringement or the illegal benefits obtained by the infringer.

\* The name and logo of China Micro Semicon (Shenzhen) Co., Ltd. are registered trademarks of the Company.

\* The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not licensed for lifesaving, life-sustaining devices or systems as critical devices. The Company reserves the right to modify the product without prior notice, please refer to the official website www.mcu.com.cn for the latest information.

### **Documentation Instructions**

This manual is the technical reference manual for the BAT32G157 microcontroller product. The technical reference manual is the application instruction material on how to use this series of products, including the structure, function description, working mode and register configuration of each functional module.

The technical reference manual is a description of all functional modules of this series of products. If you want to know the feature description of the product (that is, the functional configuration), you can refer to the respective data sheet.

The data sheet information is as follows:

BAT32G157xx: BAT32G157\_datasheet\_vx.x.x. pdf

Usually in the early stage of chip selection, you shall first check the data sheet to evaluate whether the product can meet the functional requirements of the design; after basically selecting the required product, you need to check the technical reference manual to determine whether the working mode of each functional module does meet the requirement; When determining the selection and entering the programming design stage, you need to read the technical reference manual in detail to understand the specific implementation and register configuration of each function. Refer to the data sheet for information on voltages, currents, drive capabilities, and pin assignments when designing hardware.

For a detailed description of the Cortex-M0+ core, SysTick timer and NVIC, please refer to the respective ARM documents.

|               | entation Instructions                                               |    |

|---------------|---------------------------------------------------------------------|----|

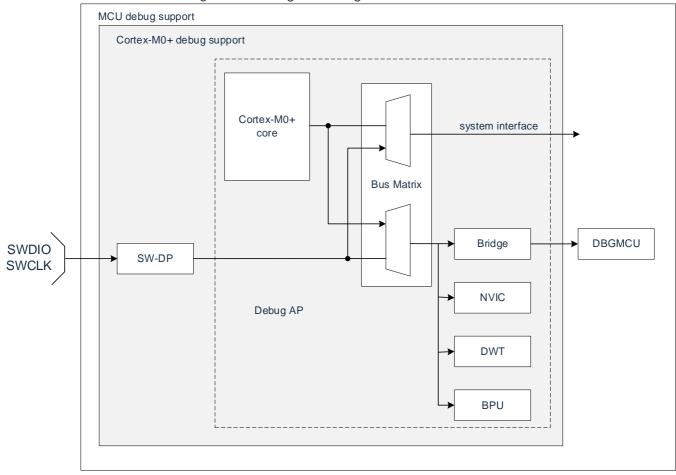

| Chapte<br>1.1 | er 1 CPU                                                            |    |

|               |                                                                     |    |

| 1.2           | Cortex-M0+ core features                                            |    |

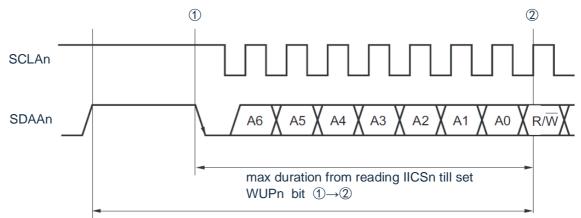

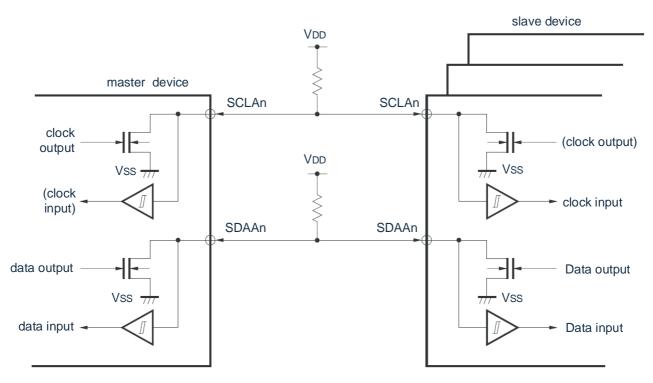

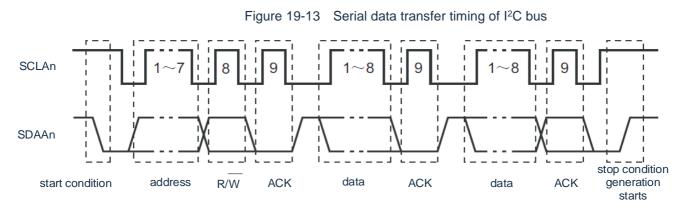

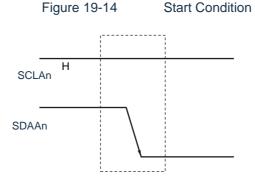

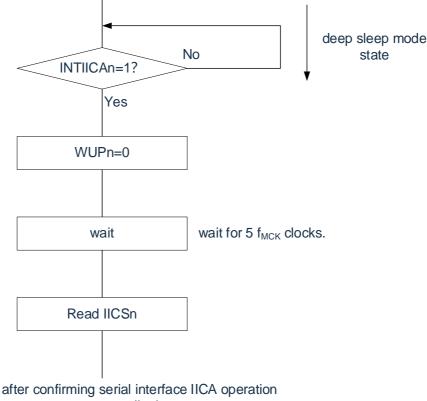

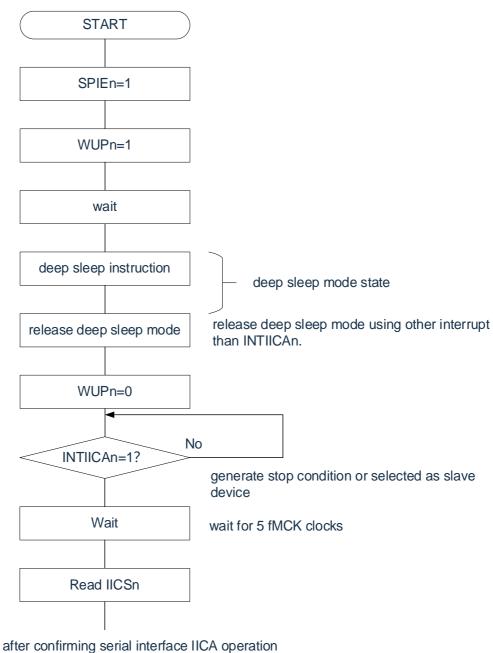

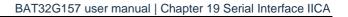

| 1.3           | Debug features                                                      |    |

| 1.4           | SWD interface pin                                                   |    |

| 1.5           | ARM reference document                                              |    |

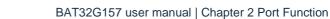

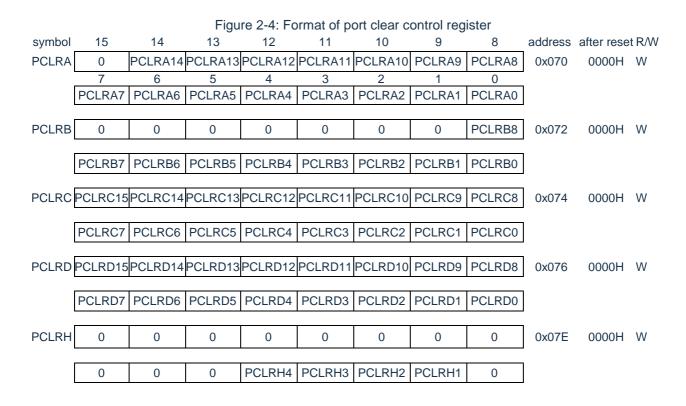

|               | er 2 Port Function                                                  |    |

| 2.1           | Port function                                                       |    |

| 2.2           | Port multiplexing function                                          |    |

| 2.3           | Registers for controlling port function                             |    |

| 2.3.1         | 5 ( )                                                               |    |

| 2.3.2         | 5 ( )                                                               |    |

| 2.3.3         |                                                                     |    |

| 2.3.4         | 5 ( )                                                               |    |

| 2.3.5         |                                                                     |    |

| 2.3.6         | Pull-down resistor selection register (PDxx)                        | 34 |

| 2.3.7         | Port output mode register (POMxx)                                   | 35 |

| 2.3.8         | B Port mode control register (PMCxx)                                | 36 |

| 2.3.9         | Port read register (PREADxx)                                        | 37 |

| 2.3.1         | 0 Port output multiplexing function configuration register (PxxCFG) | 38 |

| 2.3.1         | 1 Port input multiplexing function configuration register           | 45 |

| 2.3.1         | 2 External interrupt port selection register (INTPnPCFG)            | 50 |

| 2.3.1         | 3 USB_ DP, USB_DM port configuration registers (PMR, PRCR)          | 53 |

| 2.4           | Handling of unused ports                                            | 54 |

| 2.5           | Register settings when using the multiplexing function              | 55 |

| 2.5.1         | Basic ideas when using the multiplexed output function              | 55 |

| 2.5.2         | 2 Configuration method of multiplexed output function               | 56 |

| 2.5.3         |                                                                     |    |

| 2.5.4         |                                                                     |    |

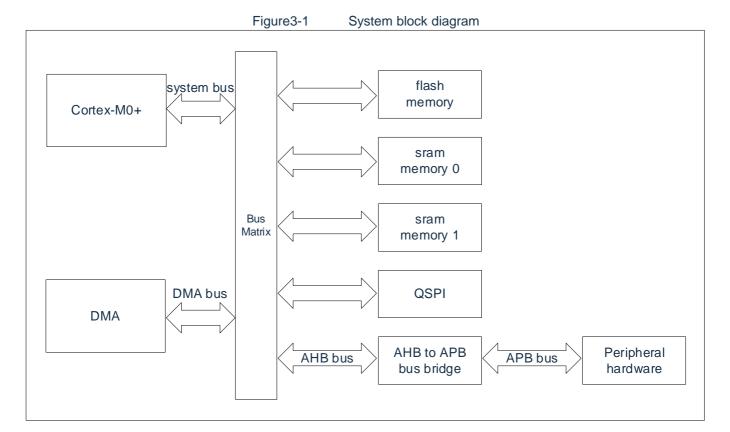

| Chapt         | er 3 System Structure                                               |    |

| 3.1           | Overview                                                            |    |

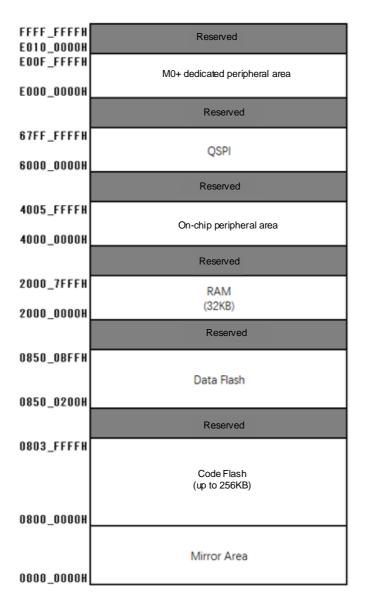

| 3.2           | System address partitioning                                         | 65 |

| 3.3           | Start configuration                                                 |    |

| 3.4           | Start switching                                                     |    |

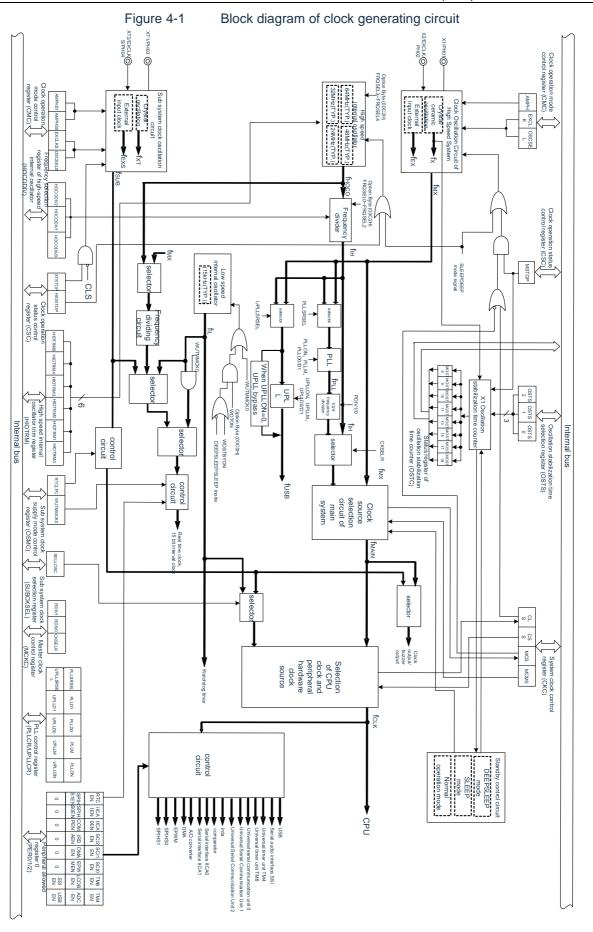

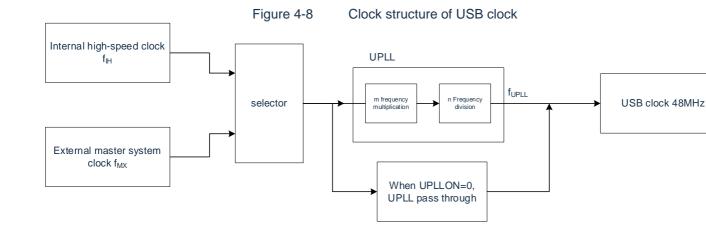

|               | er 4 Clock Generation Circuit                                       |    |

| 4.1           | Function of clock generation circuit                                |    |

| 4.2           | Structure of clock generating circuit                               |    |

| 4.3           | Registers for controlling clock generation circuit                  |    |

###

| 4.3.1   | Clock operation mode control register (CMC)                       | 75  |

|---------|-------------------------------------------------------------------|-----|

| 4.3.2   | System clock control register (CKC)                               | 77  |

| 4.3.3   | Clock operation status control register (CSC)                     |     |

| 4.3.4   | PLL control register for system clock (PLLCR)                     | 80  |

| 4.3.5   | PLL control register for USB (UPLLCR)                             | 81  |

| 4.3.6   | Oscillation stabilization time counter status register (OSTC)     | 83  |

| 4.3.7   | Oscillation stabilization time select register (OSTS)             | 85  |

| 4.3.8   | Peripheral enable registers 0, 1, 2 (PER0, PER1, PER2)            |     |

| 4.3.9   | Subsystem clock supply mode control register (OSMC)               |     |

| 4.3.10  | High-speed on-chip oscillator frequency select register(HOCODIV)  | 91  |

| 4.3.11  | High-speed on-chip oscillator trimming register (HIOTRM)          |     |

| 4.3.12  | Subsystem clock selection register (SUBCKSEL)                     |     |

| 4.3.13  | Master system clock control register (MCKC)                       |     |

| 4.4 S   | ystem clock oscillation circuit                                   | 95  |

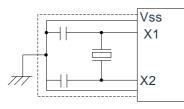

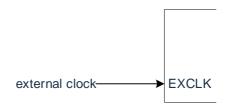

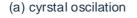

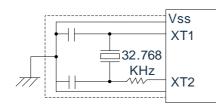

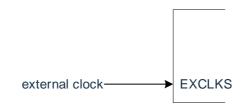

| 4.4.1   | X1 oscillation circuit                                            |     |

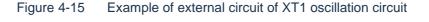

| 4.4.2   | XT1 oscillation circuit                                           |     |

| 4.4.3   | High-speed internal oscillator                                    |     |

| 4.4.4   | Low-speed internal oscillator                                     |     |

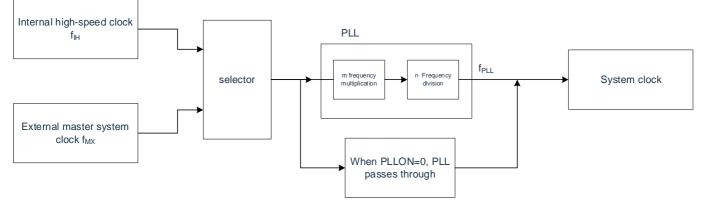

| 4.4.5   | PLL                                                               |     |

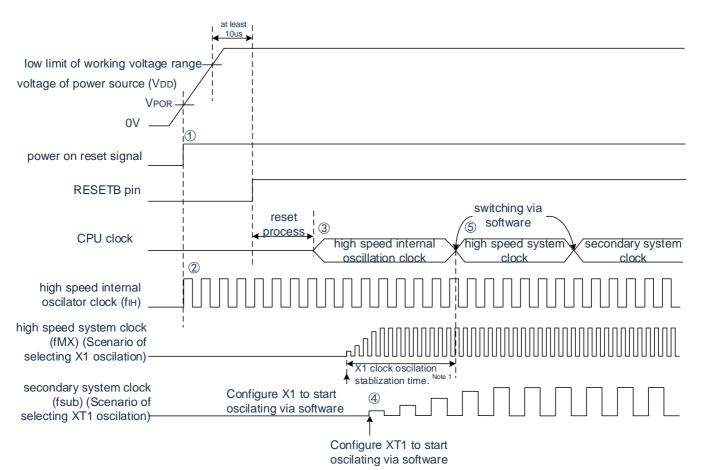

| 4.5 O   | peration of clock generation circuit                              | 100 |

| 4.6 C   | lock control                                                      |     |

| 4.6.1   | Example of high speed internal oscillator set-up                  |     |

| 4.6.2   | Example of X1 oscillation circuit setup                           | 104 |

| 4.6.3   | Example of X1 oscillation circuit setup                           | 105 |

| 4.6.4   | Example of PLL Circuit Setup                                      |     |

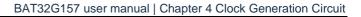

| 4.6.5   | State transition diagram of CPU clock                             | 107 |

| 4.6.6   | Conditions before CPU clock transfer and post-transfer processing | 112 |

| 4.6.7   | Time required to switch CPU clock and main system clock           | 115 |

| 4.6.8   | Conditions before clock oscillation stops                         | 116 |

| Chapter | 5 Hardware Divider                                                | 117 |

| 5.1 F   | eatures                                                           | 117 |

| 5.2 D   | escription of features                                            | 117 |

| 5.3 R   | egisters for hardware divider                                     | 117 |

| 5.3.1   | Dividend register (DIVIDEND)                                      | 118 |

| 5.3.2   | Divisor register (DIVISOR)                                        | 118 |

| 5.3.3   | Quotient register (QUOTIENT)                                      |     |

| 5.3.4   | Remainder register (REMAINDER)                                    |     |

| 5.3.5   | Status register (STATUS)                                          |     |

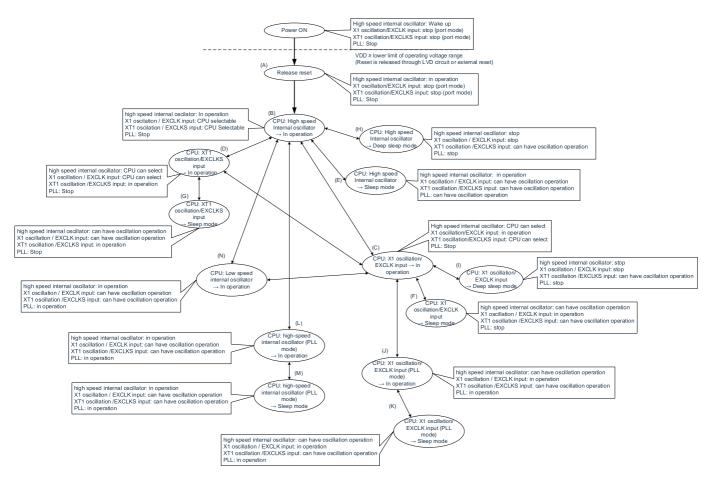

|         | 6 Universal Timer Unit (Timer4/8)                                 |     |

| 6.1 F   | unction of universal timer unit                                   |     |

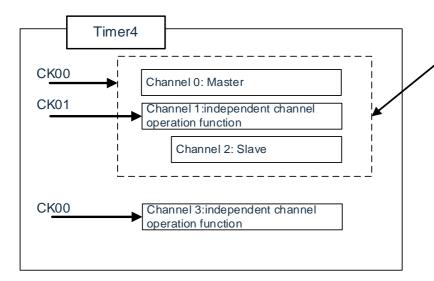

| 6.1.1     | Independent channel operation                                                             |          |

|-----------|-------------------------------------------------------------------------------------------|----------|

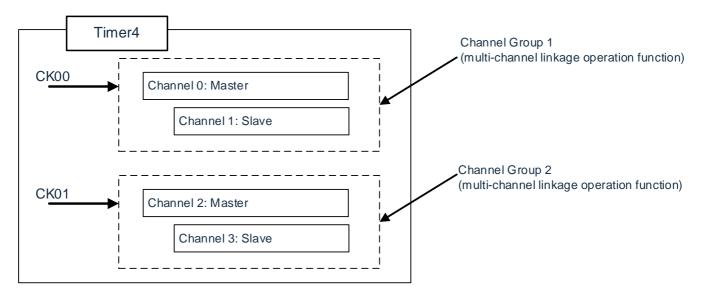

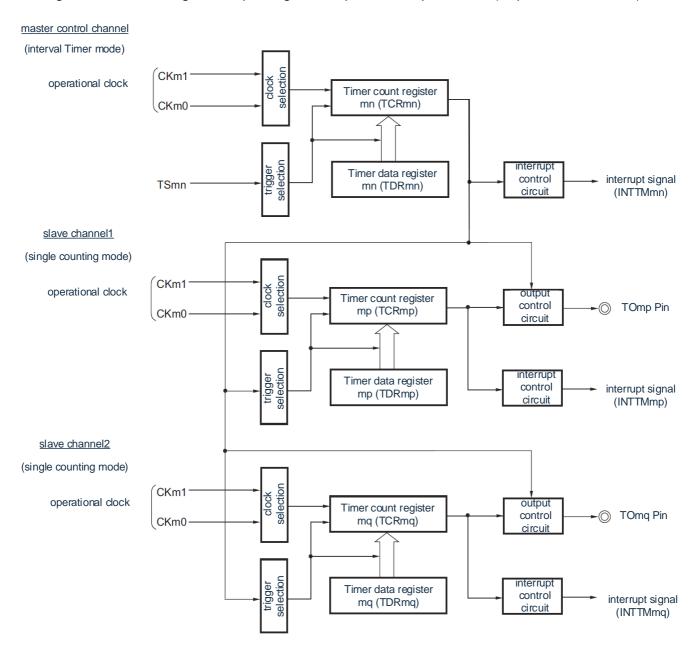

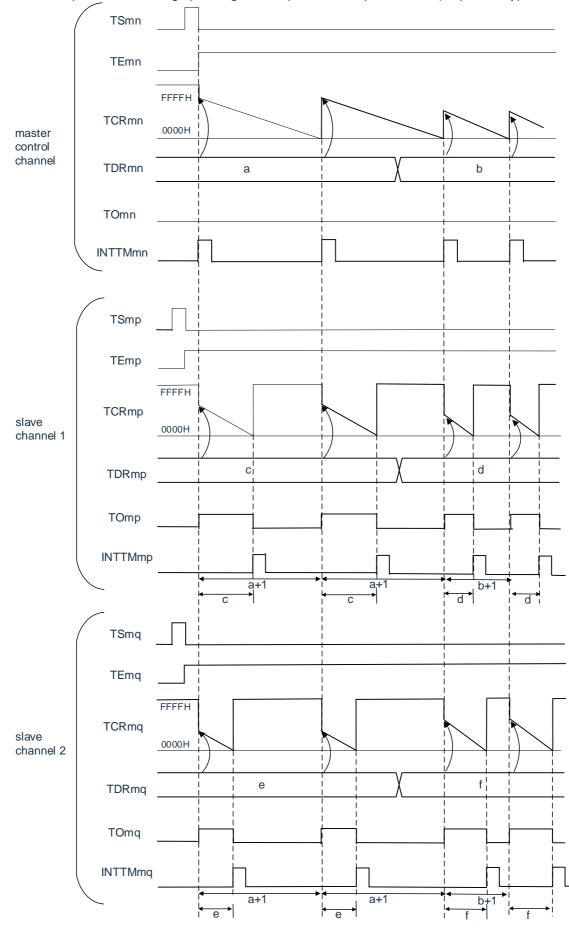

| 6.1.2     | Multi-channel linkage operation function                                                  | 124      |

| 6.1.3     | 8-bit timer operation function (channel 1 and channel 3 of unit 0 only)                   |          |

| 6.1.4     | LIN-bus support (channel 3 of unit 0 only)                                                |          |

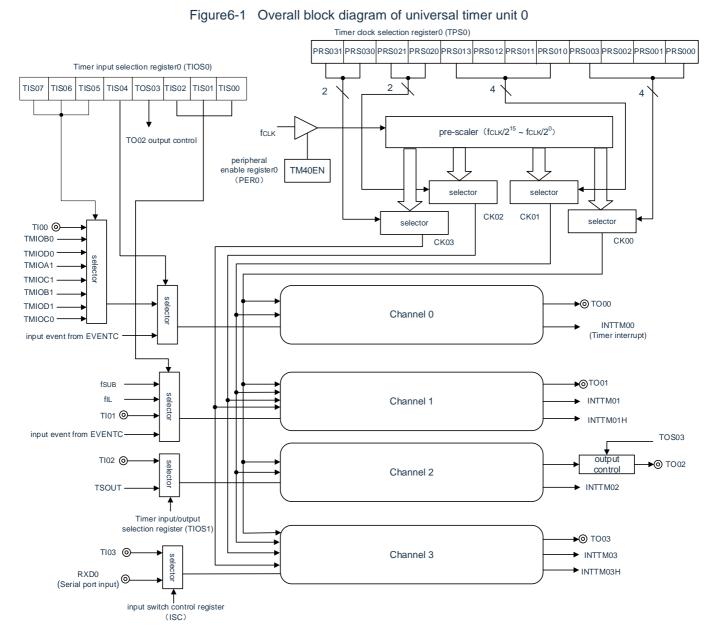

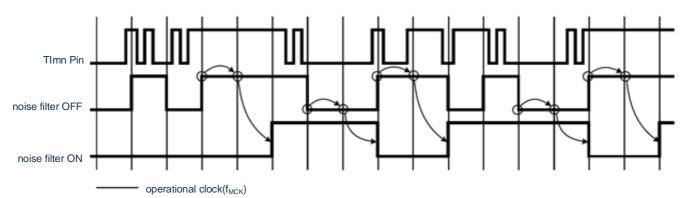

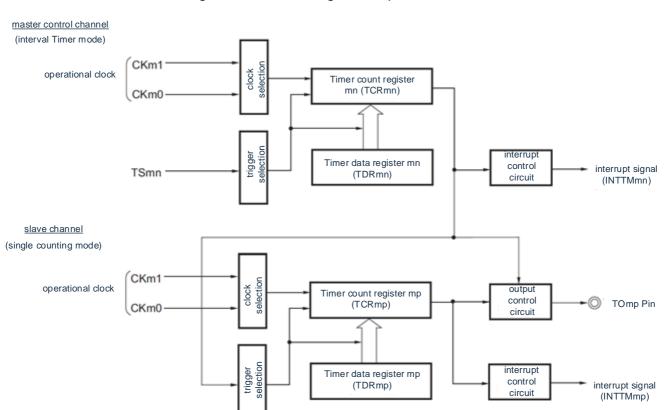

| 6.2 S     | tructure of universal timer unit                                                          | 126      |

| 6.2.1     | Universal timer unit register list                                                        | 129      |

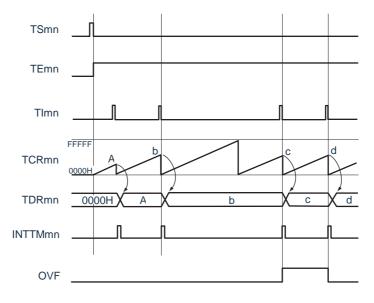

| 6.2.2     | Timer count register mn (TCRmn)                                                           | 132      |

| 6.2.3     | Timer data register mn (TDRmn)                                                            | 134      |

| 6.3 R     | egisters for controlling universal timer unit                                             | 135      |

| 6.3.1     | Peripheral enable register 0 (PER0)                                                       | 136      |

| 6.3.2     | Timer clock select register m (TPSm)                                                      | 137      |

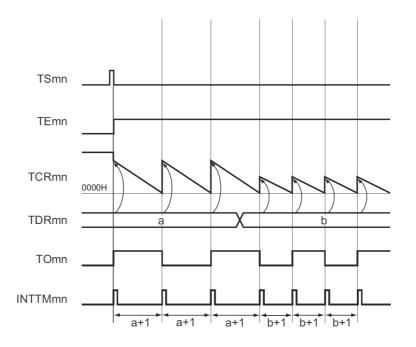

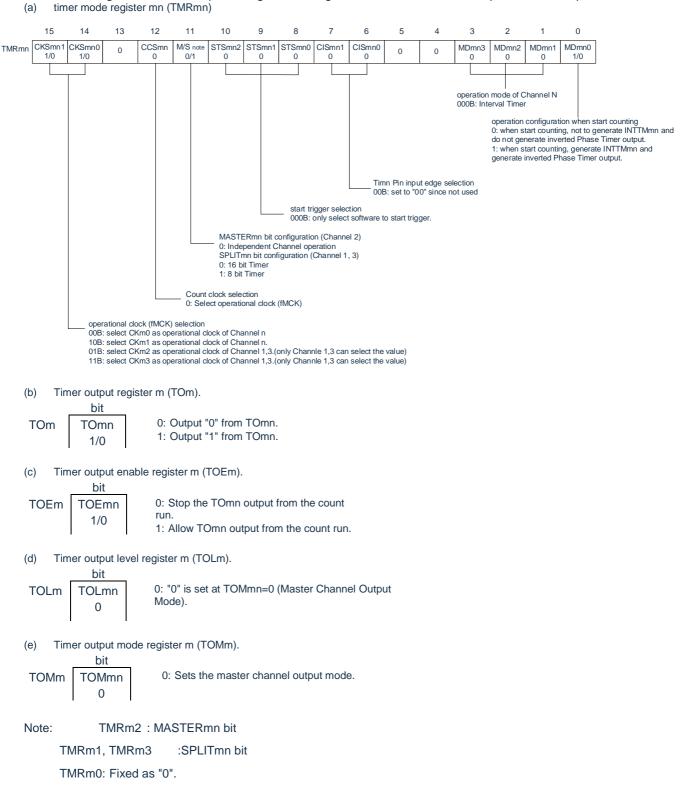

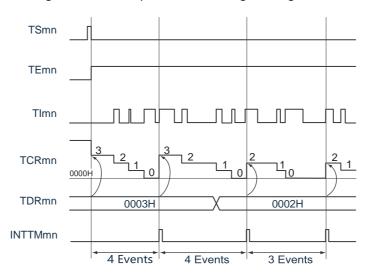

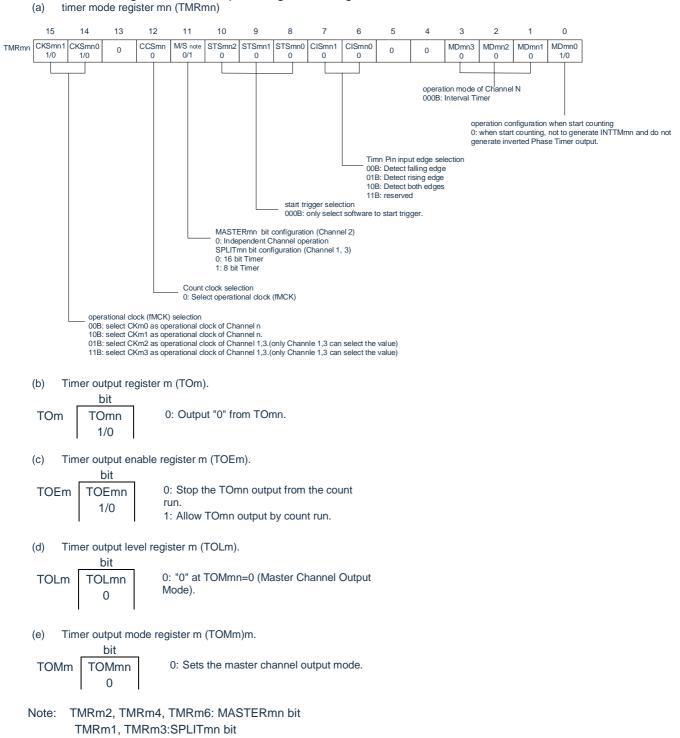

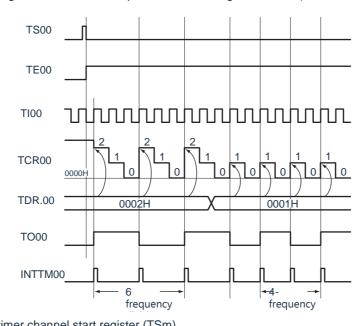

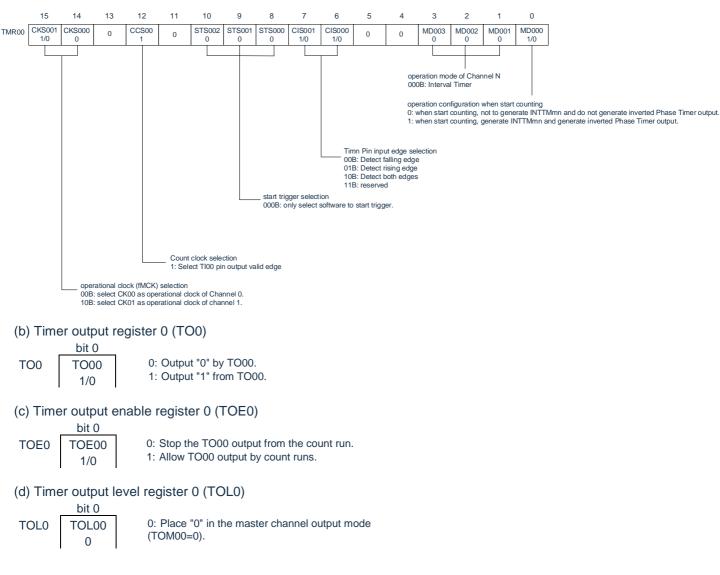

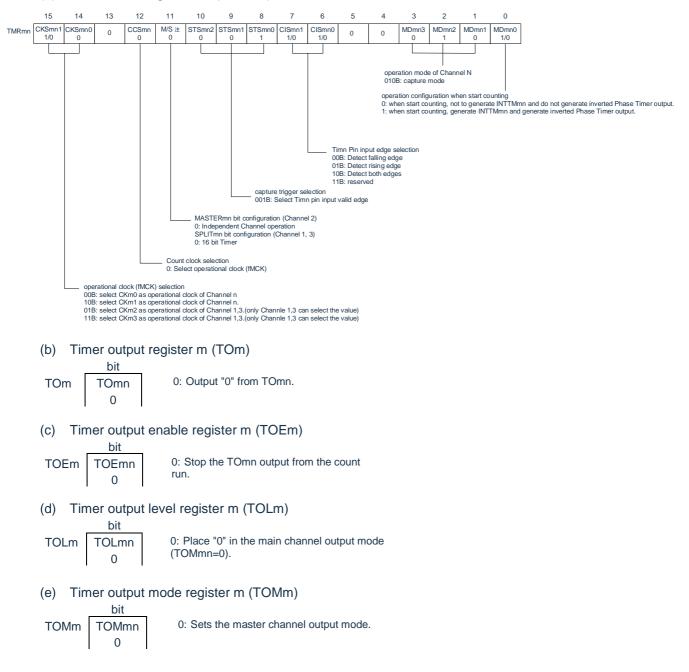

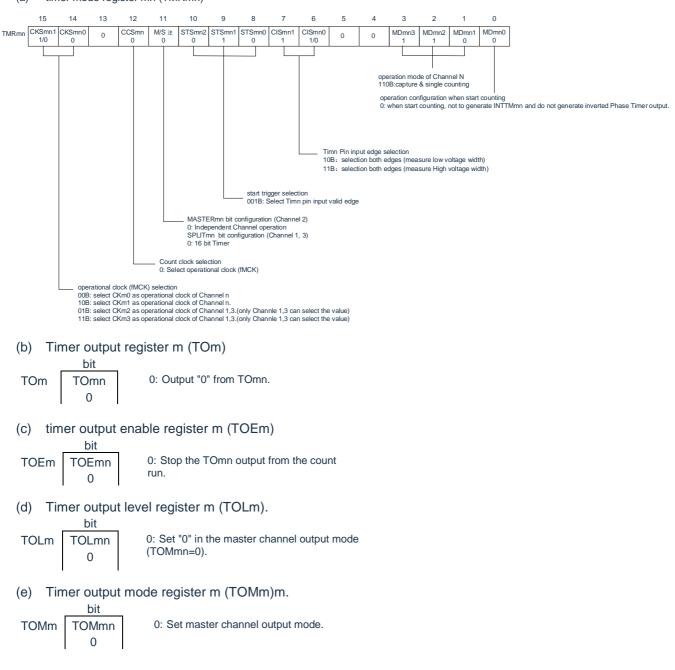

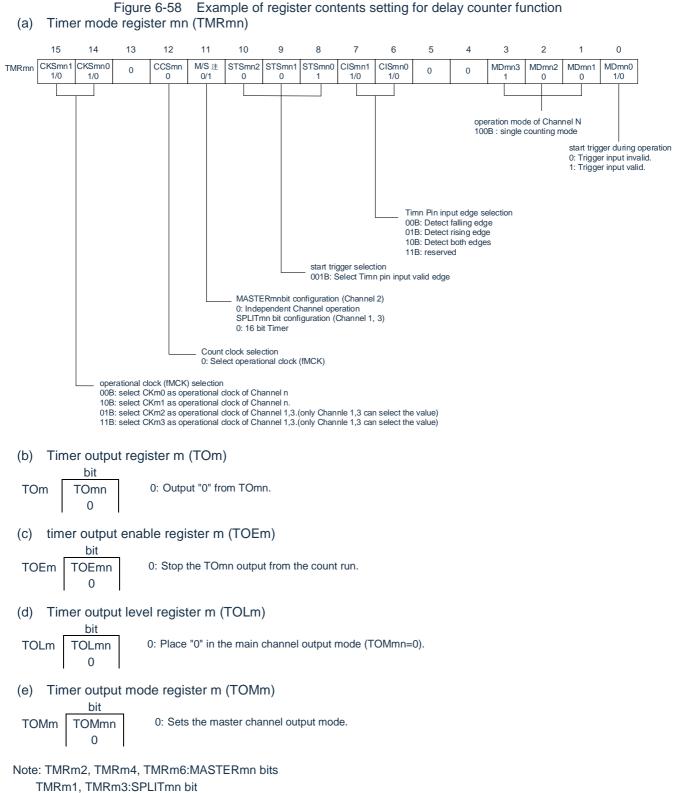

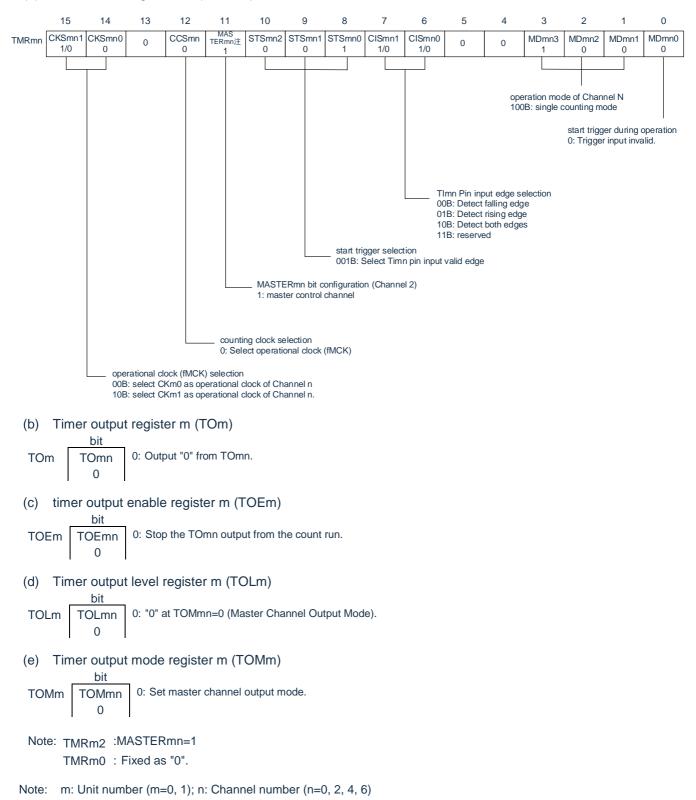

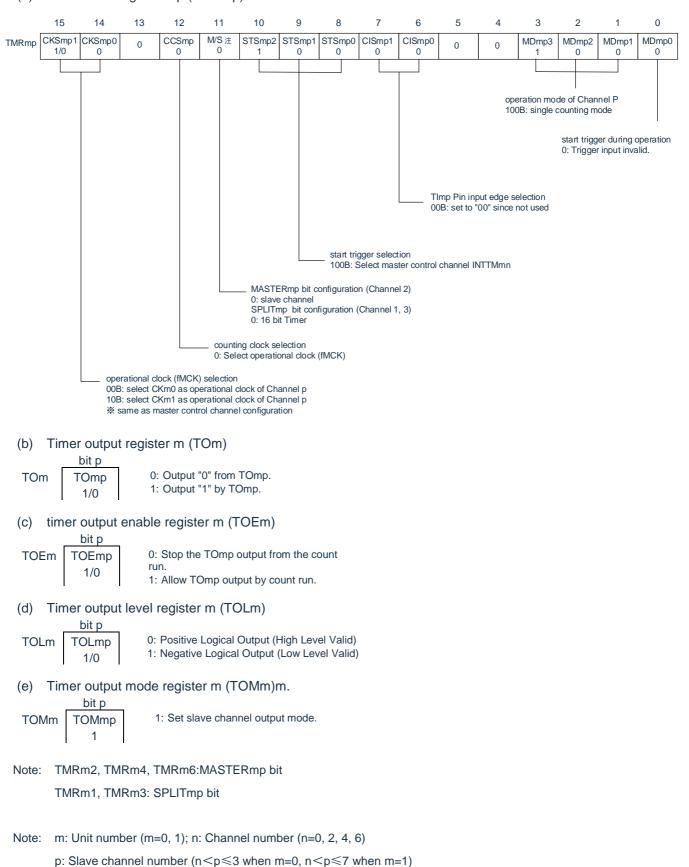

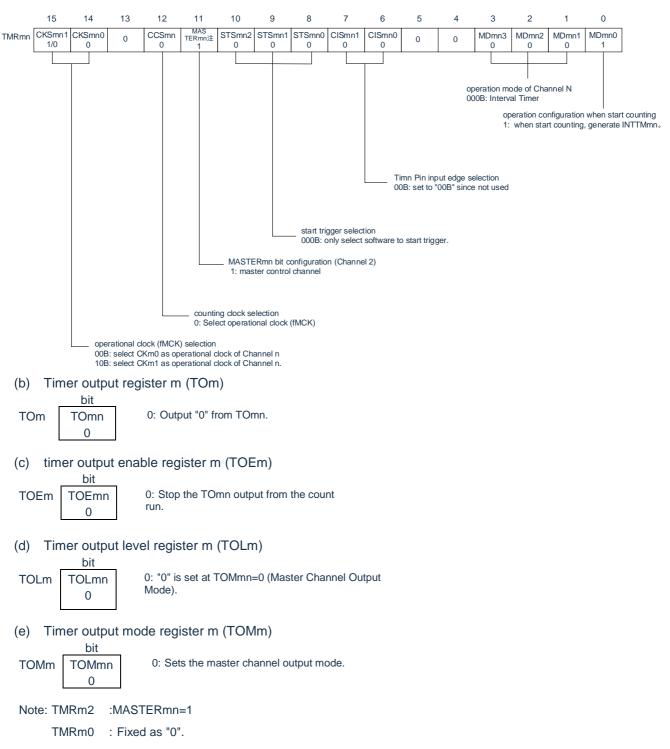

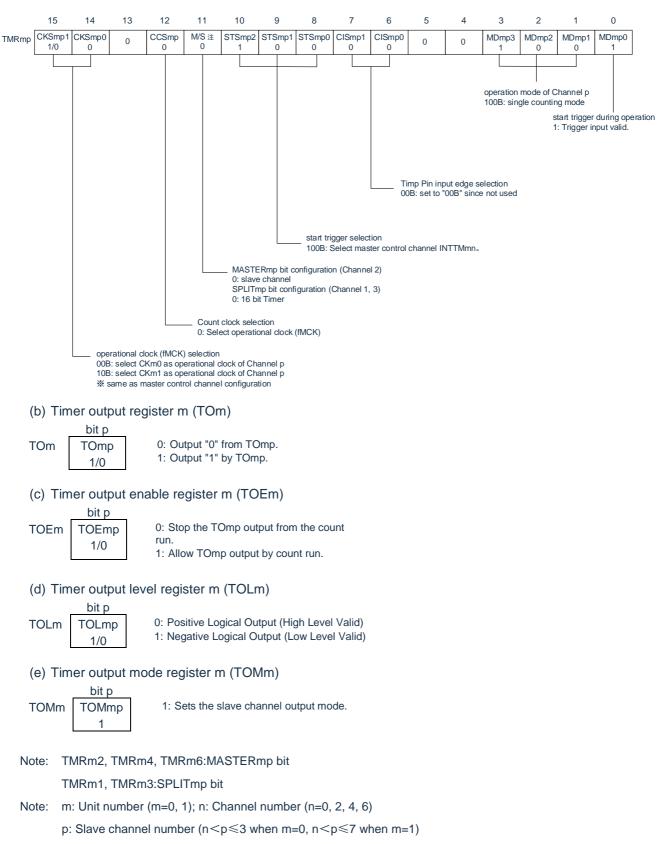

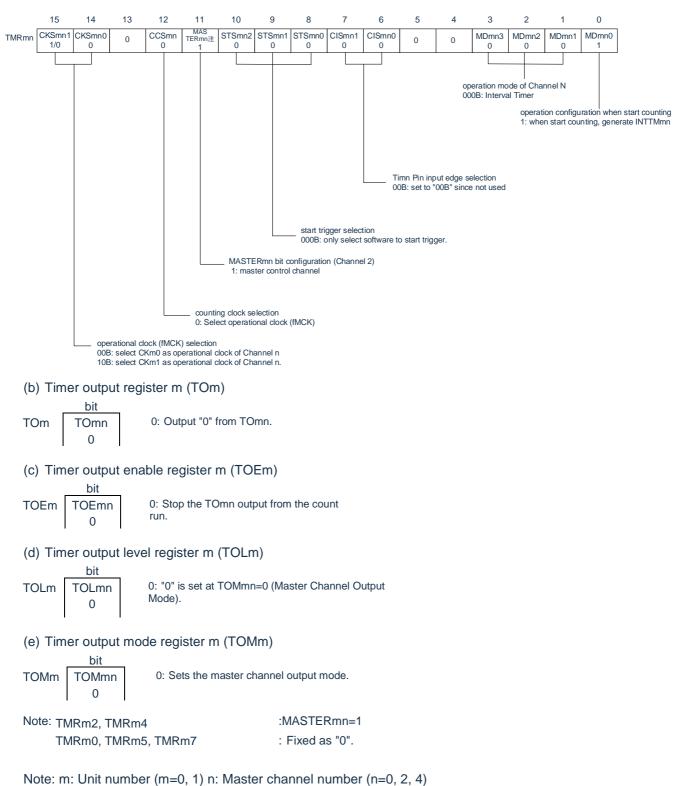

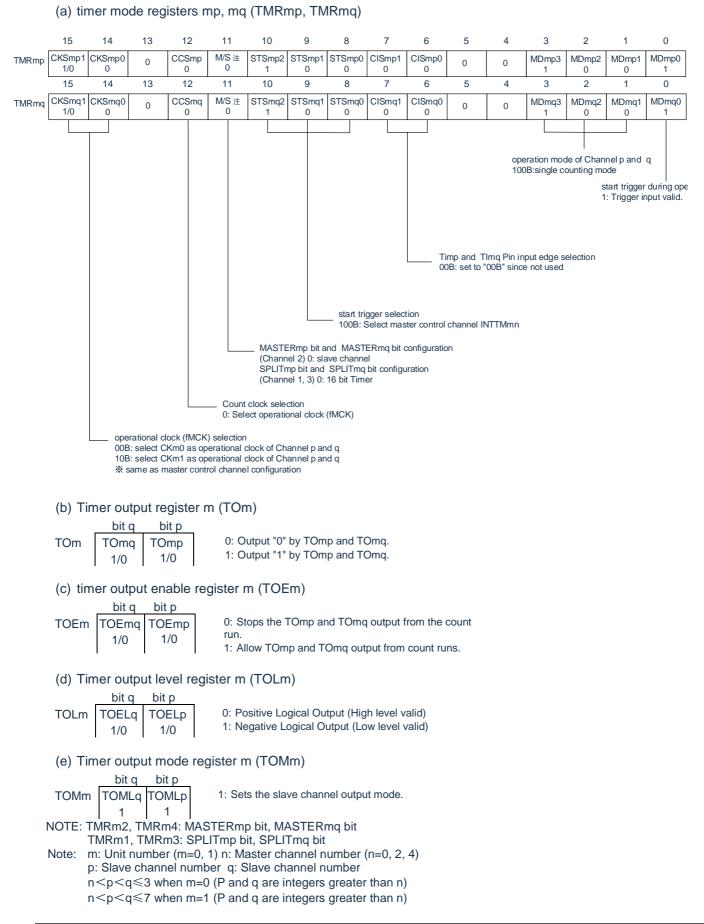

| 6.3.3     | Timer mode register mn (TMRmn)                                                            | 140      |

| 6.3.4     | Timer status register mn (TSRmn)                                                          | 144      |

| 6.3.5     | Timer channel enable status register m (TEm)                                              | 145      |

| 6.3.6     | Timer channel start register m (TSm)                                                      | 146      |

| 6.3.7     | Timer channel stop register m (TTm)                                                       | 147      |

| 6.3.8     | Timer input-output select register (TIOS0)                                                | 148      |

| 6.3.9     | Timer output enable register m (TOEm)                                                     | 149      |

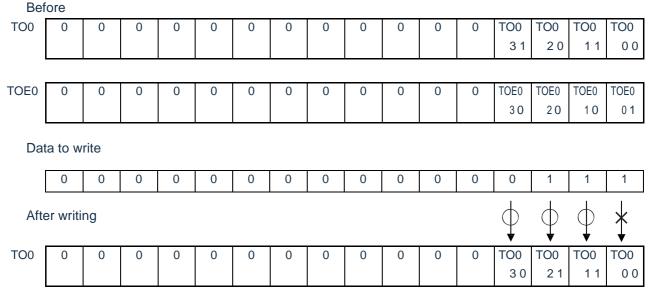

| 6.3.10    | Timer output register m (TOm)                                                             | 150      |

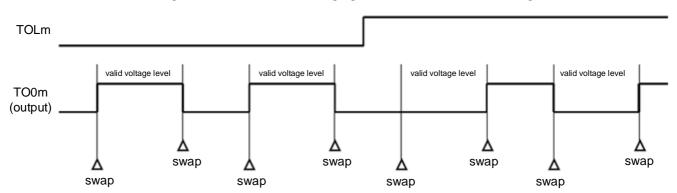

| 6.3.11    | Timer output level register m (TOLm)                                                      | 151      |

| 6.3.12    | Timer output mode register m (TOMm)                                                       | 152      |

| 6.3.13    | Input switch control register (ISC)                                                       | 153      |

| 6.3.14    | Noise filter enable register (NFEN1/NFEN2)                                                | 154      |

| 6.3.15    | Registers for controlling timer input/output pin port function                            | 155      |

| 6.4 B     | asic rules for universal timer units                                                      | 156      |

| 6.4.1     | Basic prinicpal of multi-channel linkage operation function                               | 156      |

| 6.4.2     | Timer channel start register m (TSm)                                                      | 158      |

| 6.4.3     | Basic principle for the 8-bit timer operation function (channel 1 and channel 3 of unit 0 | only)159 |

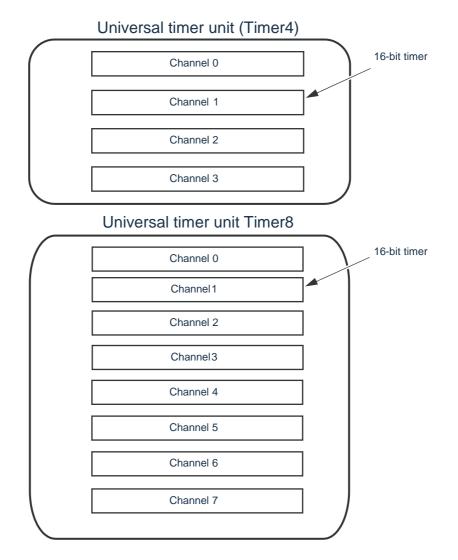

| 6.5 O     | Operation of counter                                                                      | 160      |

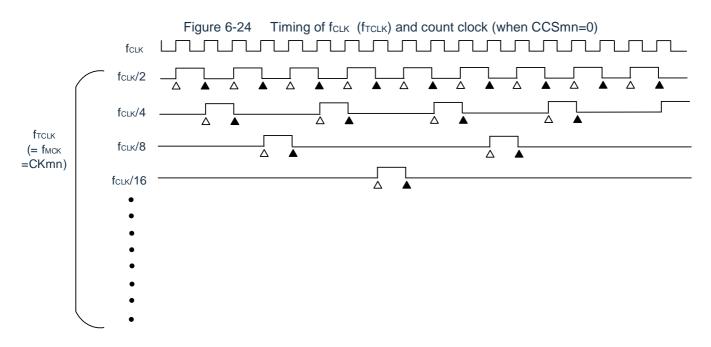

| 6.5.1     | Count clock (f <sub>TCLK</sub> )                                                          | 160      |

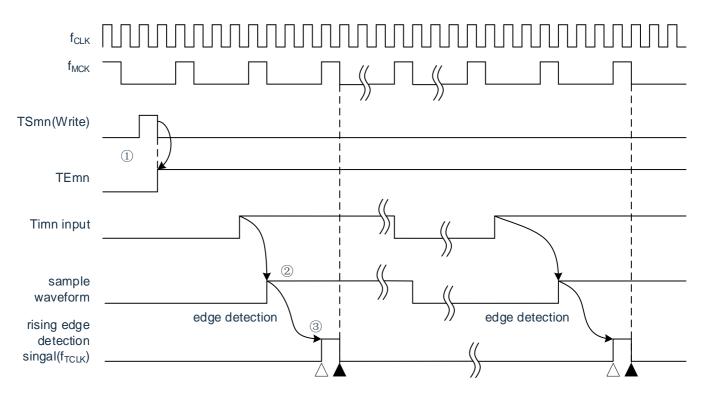

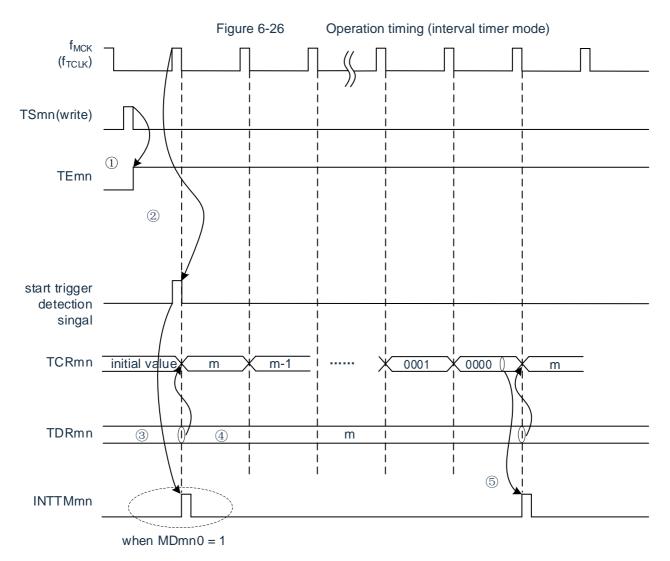

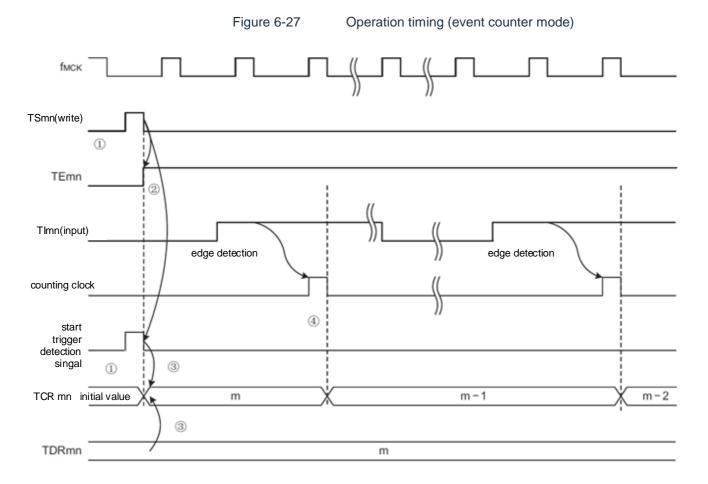

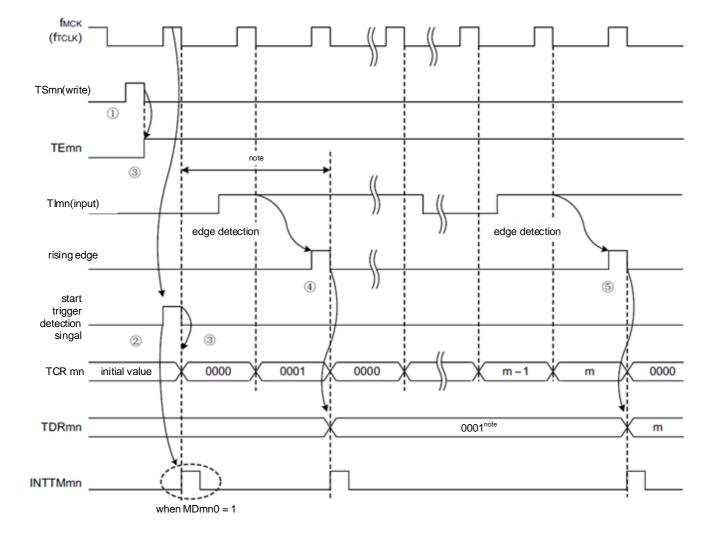

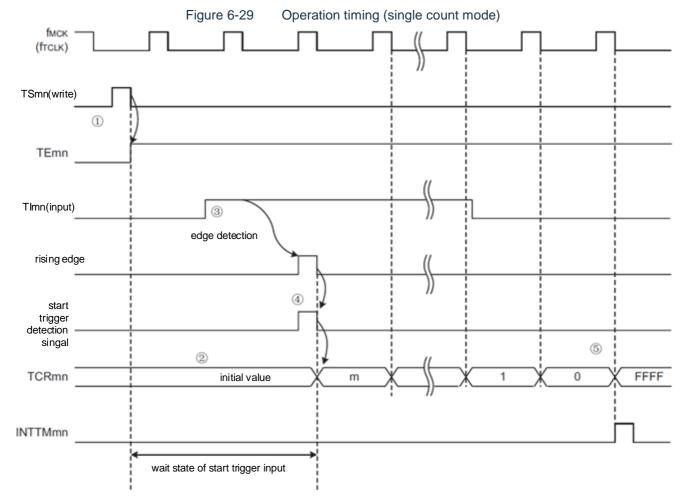

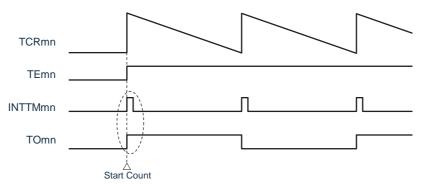

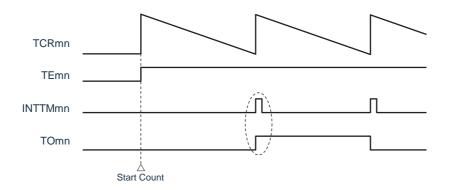

| 6.5.2     | Start timing of counter                                                                   | 162      |

| 6.5.3     | Operation of counter                                                                      | 163      |

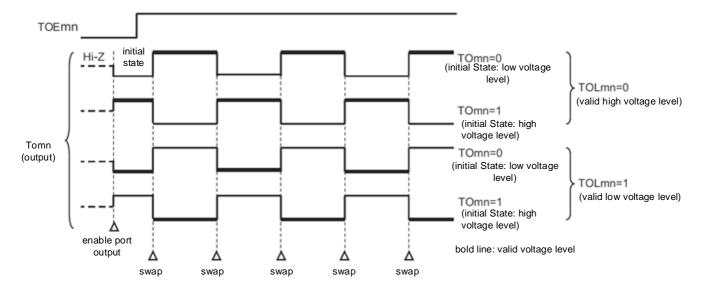

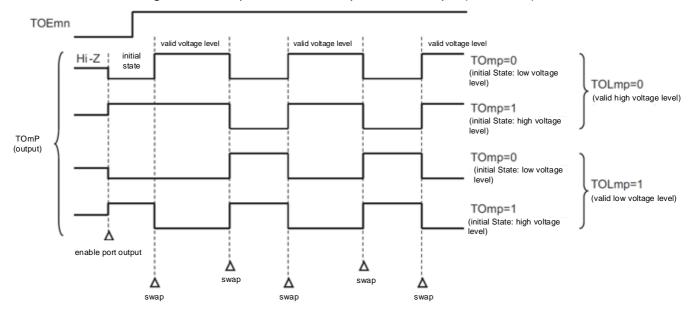

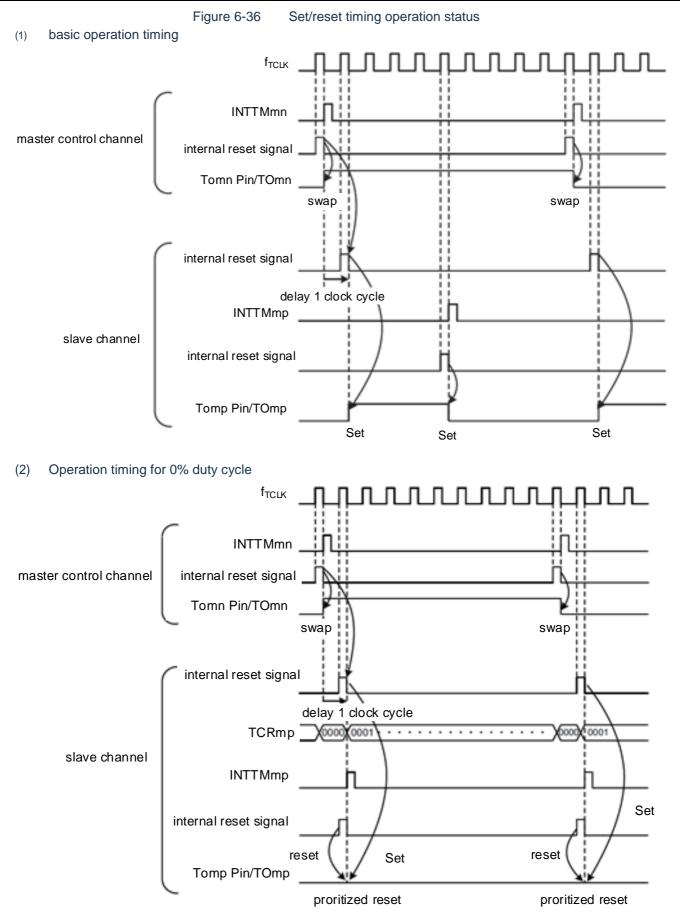

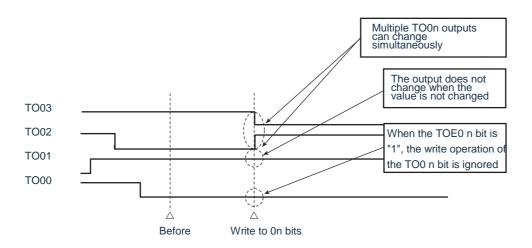

| 6.6 C     | control of channel output (TOmn pin)                                                      | 168      |

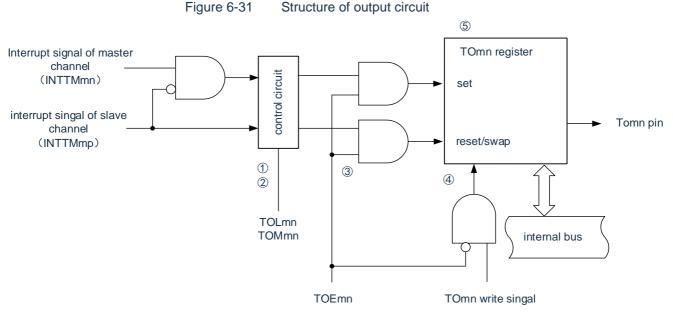

| 6.6.1     | Structure of TOmn pin output circuit                                                      | 168      |

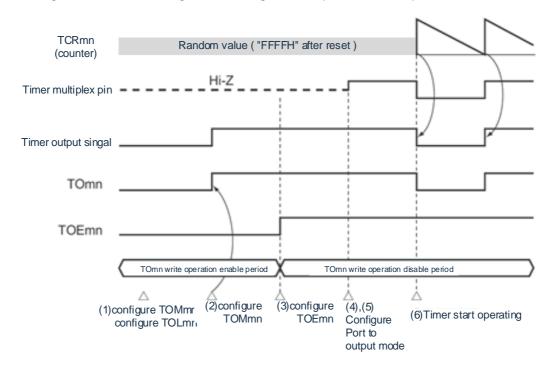

| 6.6.2     | TOmn pin output configuration                                                             | 169      |

| 6.6.3     | Cautions for channel output operation                                                     | 170      |

| 6.6.4     | One-time operation of TOmn bit                                                            | 175      |

| 6.6.5     | Timer interrupt and TOmn pin output when counting starts                                  | 176      |

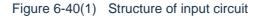

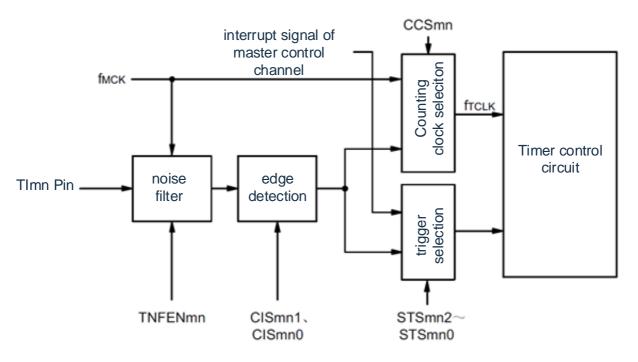

| 6.7 C     | Control of timer input (TImn)                                                             | 177      |

| 6.7.1     | Structure of TImn pin input circuit                                                       | 177      |

| /w.mcu.co |                                                                                           | V1.0.5   |

###

| 6.7.2   | Noise filter                                                              | 177 |

|---------|---------------------------------------------------------------------------|-----|

| 6.7.3   | Precautions when operating channel inputs                                 | 178 |

| 6.8 Ir  | dependent channel operation function of universal timer unit              | 179 |

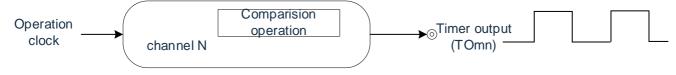

| 6.8.1   | Operation as interval timer/square wave output                            | 179 |

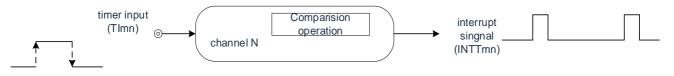

| 6.8.2   | Operation as external event counter                                       |     |

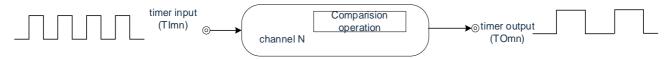

| 6.8.3   | Operation as frequency divider                                            |     |

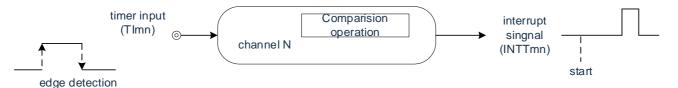

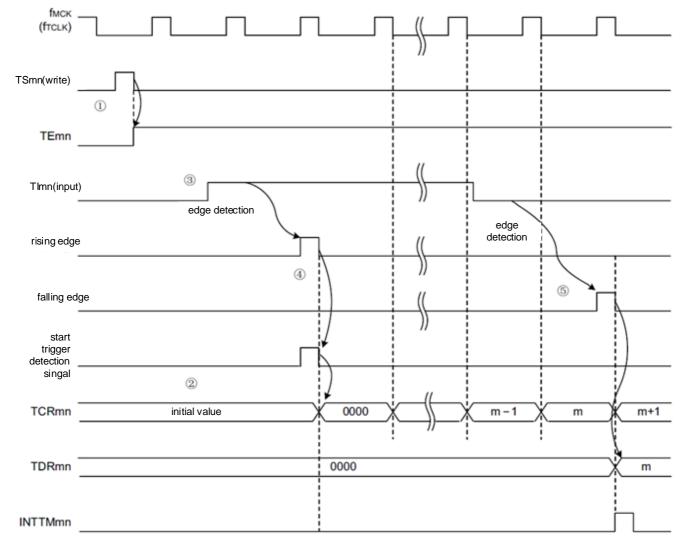

| 6.8.4   | Operation as input pulse interval measurement                             |     |

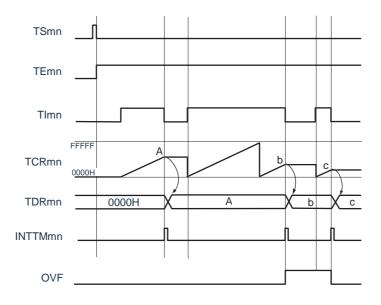

| 6.8.5   | Operation as voltage high and low level width measurement of input signal | 192 |

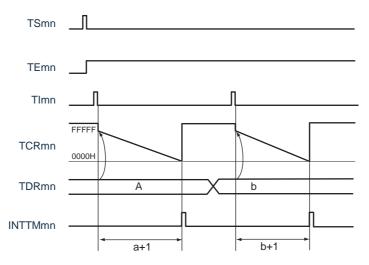

| 6.8.6   | Operation as delay counter                                                | 196 |

| 6.9 N   | ulti-channel linkage operation function of universal timer unit           | 199 |

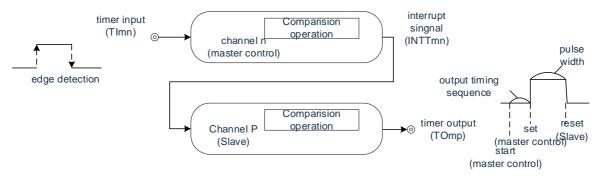

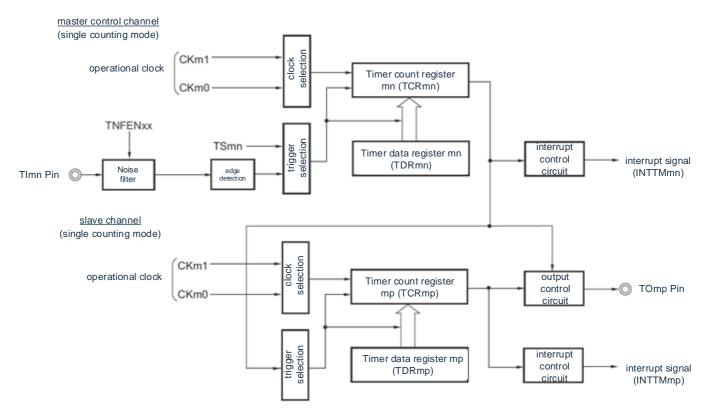

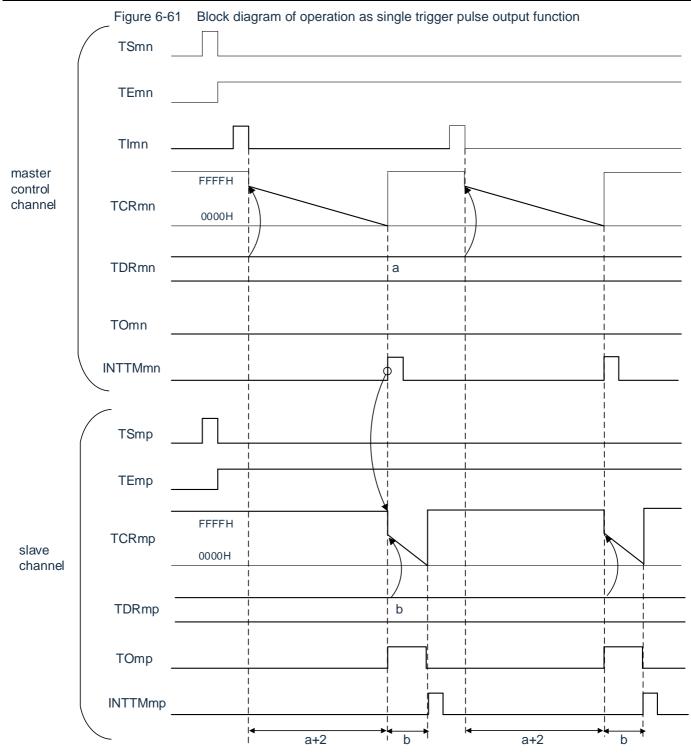

| 6.9.1   | Operation as single trigger pulse output function                         | 199 |

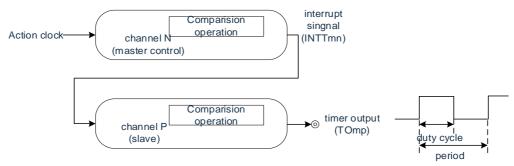

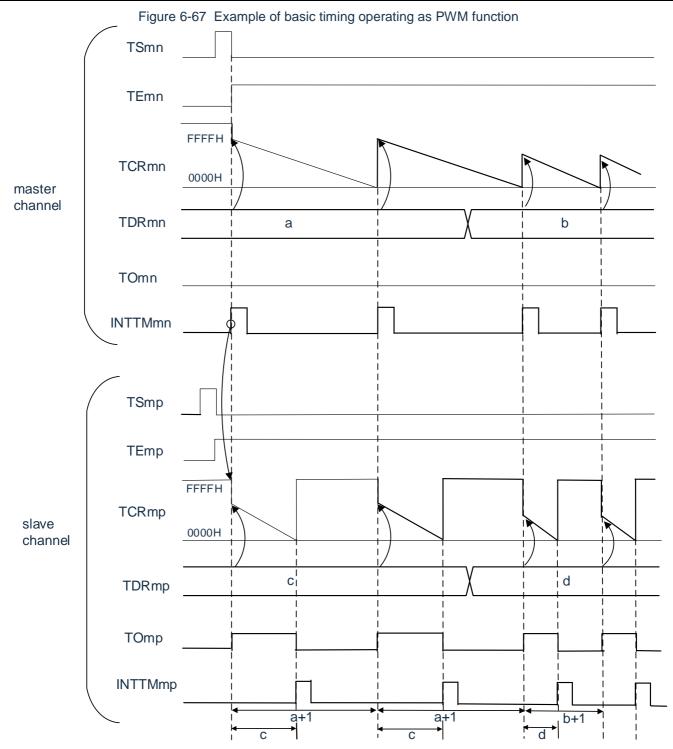

| 6.9.2   | Operation as PWM function                                                 | 206 |

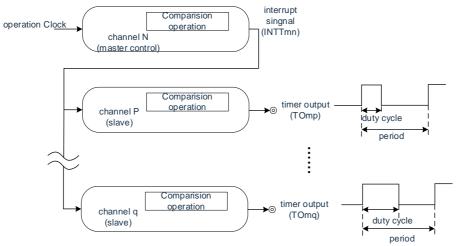

| 6.9.3   | Operation as multiple PWM output function                                 | 213 |

| 6.10 C  | autions when using the universal timer unit                               | 221 |

| 6.10.1  | Cautions when using timer output                                          | 221 |

| Chapter | 7 EPWM Output Control Circuit                                             | 222 |

| 7.1 F   | unction of EPWM output control circuit                                    |     |

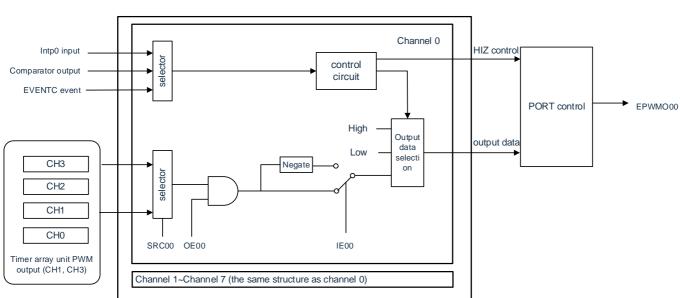

| 7.2 S   | tructure of output control circuit                                        |     |

| 7.3 R   | egisters for controlling EPWM output control circuit                      | 223 |

| 7.3.1   | Peripheral enable register 1 (PER1)                                       | 224 |

| 7.3.2   | EPWM input source selection register (EPWMSRC)                            | 224 |

| 7.3.3   | EPWM output control register (EPWMCTL)                                    |     |

| 7.3.4   | EPWM force truncated input select register (EPWMSTC)                      |     |

| 7.3.5   | EPWM force truncated output select register (EPWMSTL)                     |     |

| 7.3.6   | EPWM status register (EPWMSTR)                                            |     |

| 7.3.7   | Control register for the port function of the EPWM output pin             |     |

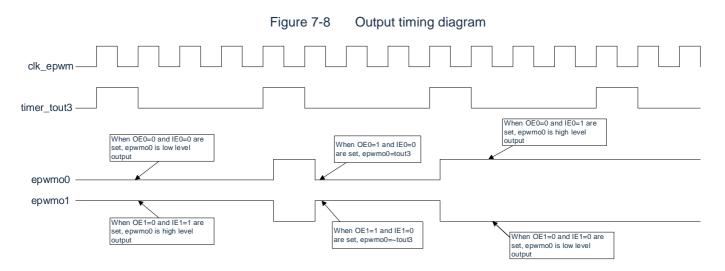

| 7.4 O   | peration of EPWM output control circuit                                   |     |

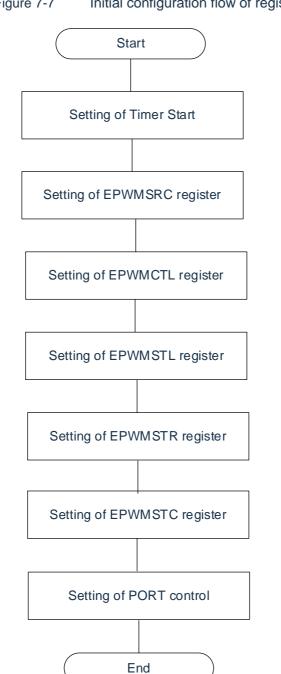

| 7.4.1   | Initial setup                                                             |     |

| 7.4.2   | Normal operation                                                          |     |

| 7.4.3   | Force truncation processing                                               |     |

| 7.5 C   | ontrol example of brushless DC motor                                      |     |

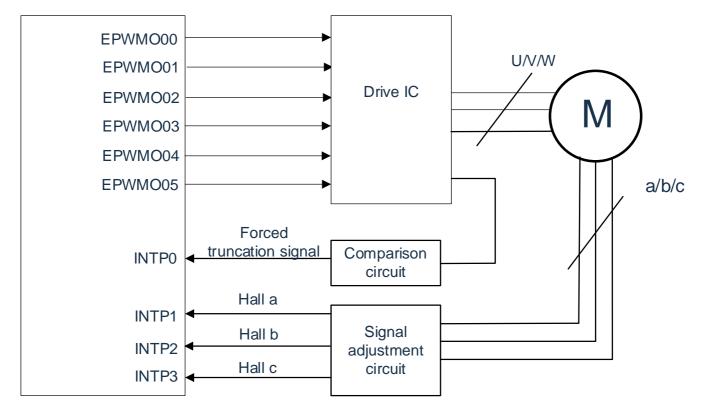

| 7.5.1   | Example of hardware connections                                           | 232 |

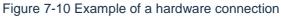

| 7.5.2   | Control timing of three-phase brushless DC motors                         |     |

| 7.5.3   | Example of register setting                                               | 234 |

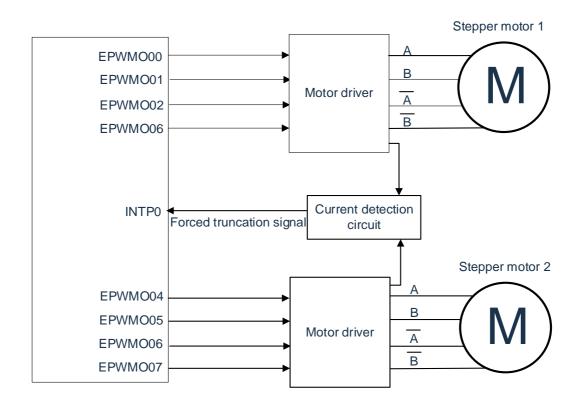

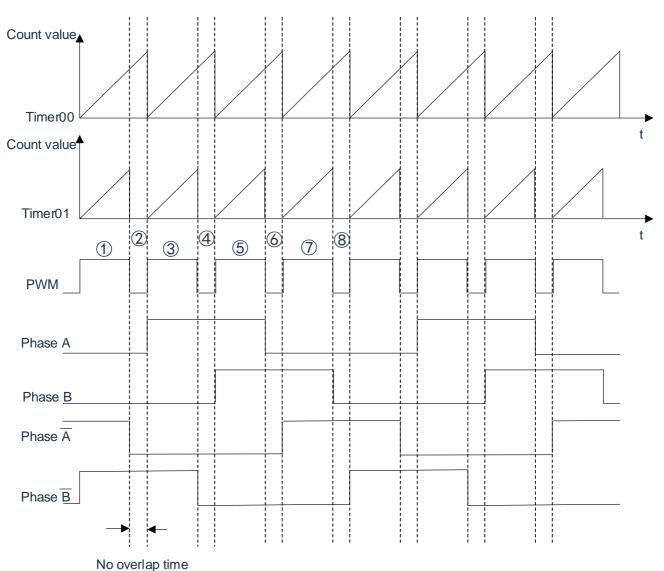

| 7.6 E   | xample of stepper motor control                                           | 235 |

| 7.6.1   | Example of a hardware connection                                          | 235 |

| 7.6.2   | Control method                                                            | 236 |

| 7.6.3   | Example of register setting                                               |     |

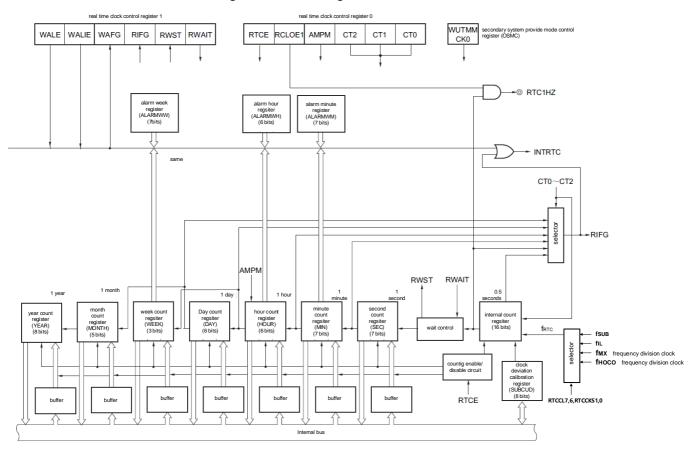

|         | 8 Real-Time Clock                                                         |     |

| 8.1 F   | unction of real-time clock                                                |     |

| 8.2 S   | tructure of real-time clock                                                        | 238     |

|---------|------------------------------------------------------------------------------------|---------|

| 8.3 R   | egister for controlling real-time clock                                            | 240     |

| 8.3.1   | Peripheral enable register 0 (PER0)                                                | 241     |

| 8.3.2   | Real-time clock selection register (RTCCL)                                         | 242     |

| 8.3.3   | Real-time clock control register 0 (RTCC0)                                         | 243     |

| 8.3.4   | Real-time clock control register 1 (RTCC1)                                         | 244     |

| 8.3.5   | Clock error correction register (SUBCUD)                                           | 246     |

| 8.3.6   | Second count register (SEC)                                                        | 247     |

| 8.3.7   | Minute count register (MIN)                                                        | 247     |

| 8.3.8   | Hour count register (HOUR)                                                         | 248     |

| 8.3.9   | Day count register (DAY)                                                           | 250     |

| 8.3.10  | Week count register (WEEK)                                                         | 251     |

| 8.3.11  | Month count register (MONTH)                                                       | 252     |

| 8.3.12  | Year count register (YEAR)                                                         | 252     |

| 8.3.13  | Alarm minute register (ALARMWM)                                                    | 253     |

| 8.3.14  | Alarm hour register (ALARMWH)                                                      | 253     |

| 8.3.15  | Alarm clock week register (ALARMWW)                                                | 253     |

| 8.3.16  | Port mode register and port register                                               | 254     |

| 8.4 C   | Operation of real-time clock                                                       | 255     |

| 8.4.1   | Start of real-time clock operation                                                 | 255     |

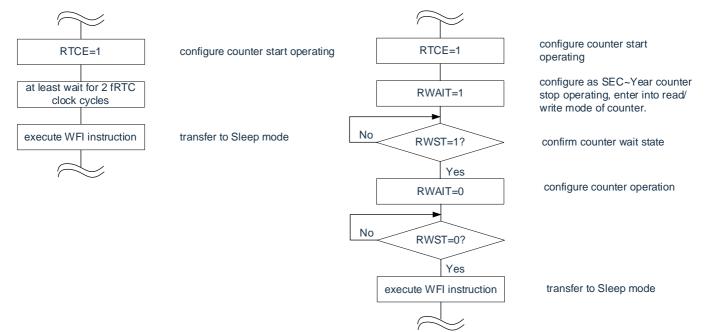

| 8.4.2   | Shifting to sleep mode after starting operation                                    | 256     |

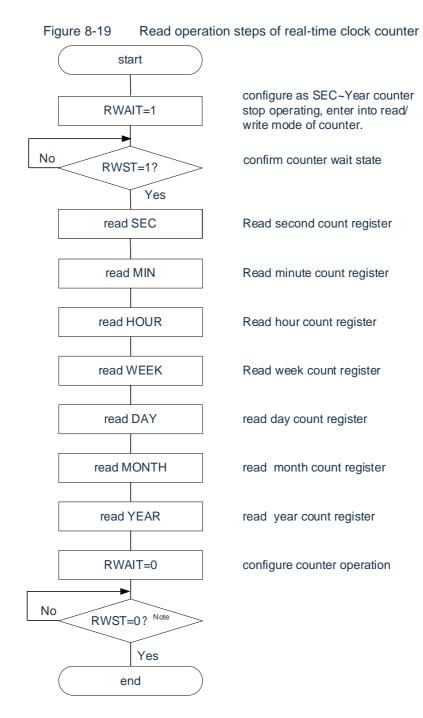

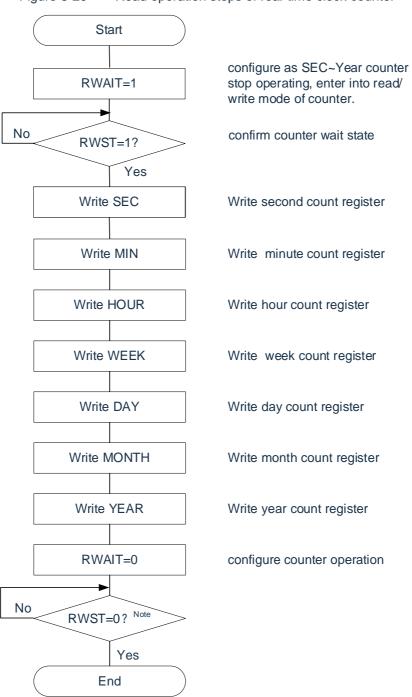

| 8.4.3   | Real-time clock counter reading and writing                                        | 257     |

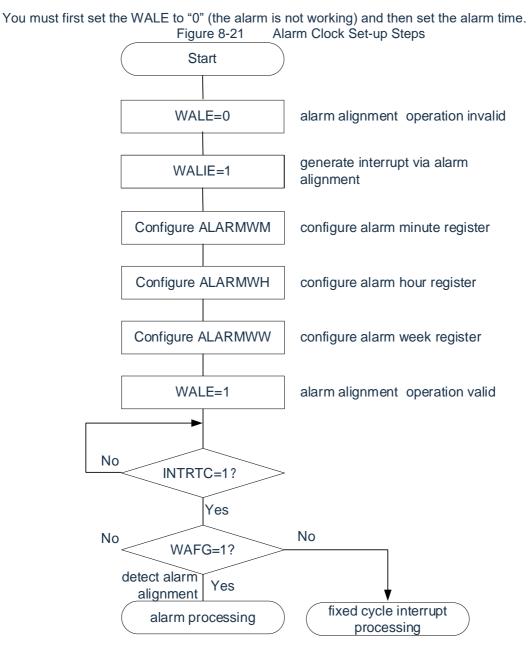

| 8.4.4   | Alarm setting for real-time clock                                                  | 259     |

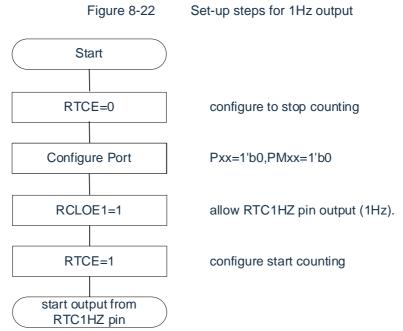

| 8.4.5   | 1 Hz output of real-time clock                                                     | 260     |

| 8.4.6   | Example of clock deviation calibration for a real-time clock                       | 261     |

| Chapter | <sup>•</sup> 9 15-Bit Interval Timer                                               | 263     |

| 9.1 F   | unction of 15-bit interval timer                                                   |         |

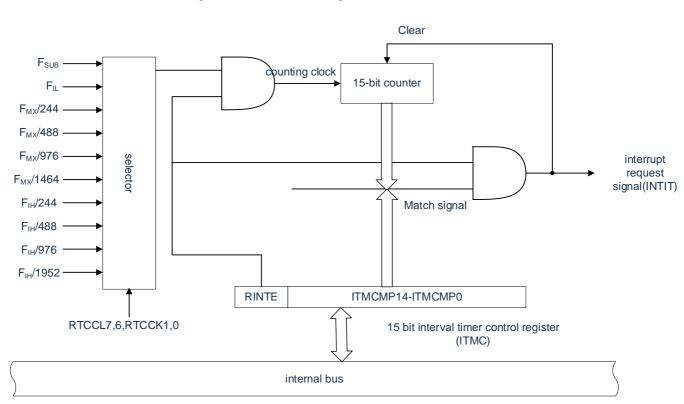

| 9.2 S   | tructure of 15-bit interval timer                                                  |         |

| 9.3 R   | egisters for controlling 15-bit interval timer                                     | 264     |

| 9.3.1   | Peripheral enable register 0 (PER0)                                                | 264     |

| 9.3.2   | Real-time clock selection register (RTCCL)                                         | 265     |

| 9.3.3   | 15-bit interval timer control register (ITMC)                                      | 266     |

| 9.4 C   | peration of 15-bit interval timer                                                  | 267     |

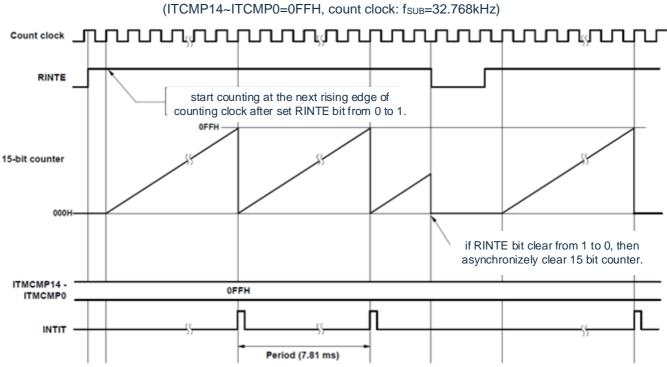

| 9.4.1   | Operation timing of 15-bit interval timer                                          | 267     |

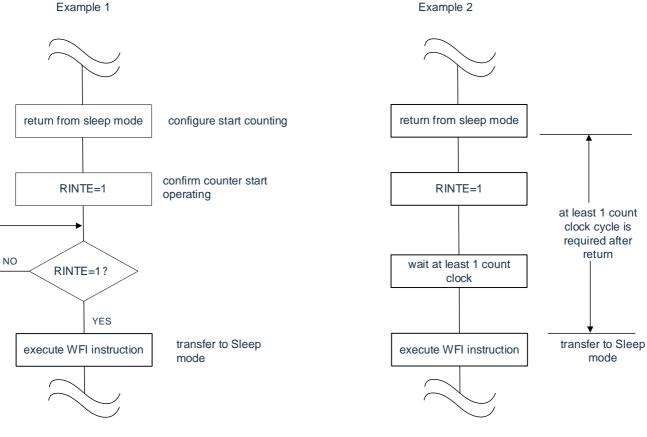

| 9.4.2   | Start of count operation and re-enter to sleep mode after returned from sleep mode | 268     |

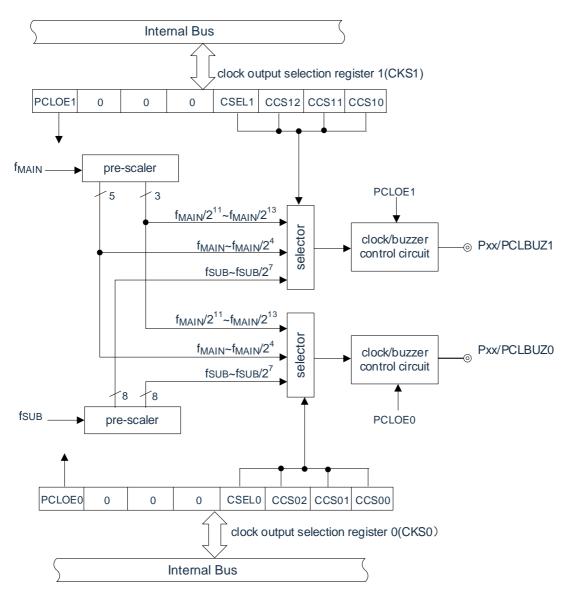

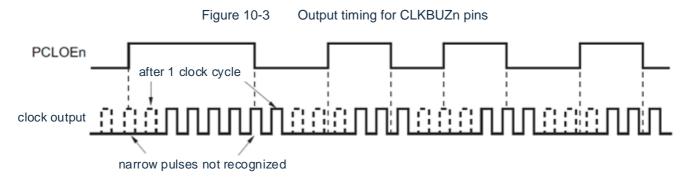

| Chapter | <sup>1</sup> 10 Clock Output/Buzzer Output Control Circuit                         | 269     |

| 10.1 F  | unction of clock output/buzzer output control circuit                              | 269     |

| 10.2 S  | tructure of clock output/buzzer output control circuit                             | 270     |

| 10.2.1  | Clock output selection register n (CKSn)                                           | 270     |

| 10.2.2  | Registers for controlling clock output/buzzer output pin port                      |         |

|         | 2 Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z                                            | \/1.0.5 |

###

| 10.3 Operation of clock output/buzzer output control circuit                | 273 |

|-----------------------------------------------------------------------------|-----|

| 10.4 Cautions for clock output/buzzer output control circuit                | 273 |

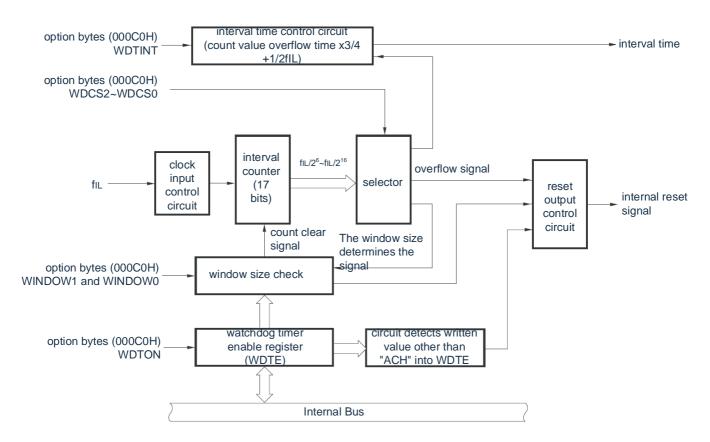

| Chapter 11 Watchdog Timer                                                   | 274 |

| 11.1 Function of watchdog timer                                             |     |

| 11.2 Structure of watchdog timer                                            | 274 |

| 11.3 Registers for controlling watchdog timer                               |     |

| 11.3.1 Watchdog timer enable register (WDTE)                                |     |

| 11.3.2 LOCKUP control register (LOCKCTL) and its protection register (PRCR) | 277 |

| 11.4 Operation of watchdog timer                                            | 278 |

| 11.4.1 Operation control of watchdog timer                                  |     |

| 11.4.2 Setting of overflow time of watchdog timer                           |     |

| 11.4.3 Watchdog timer window settings during opening                        | 281 |

| 11.4.4 Setting of watchdog timer interval interrupt                         |     |

| 11.4.5 Operation of watchdog timer during LOCKUP                            |     |

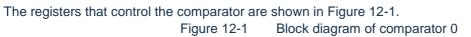

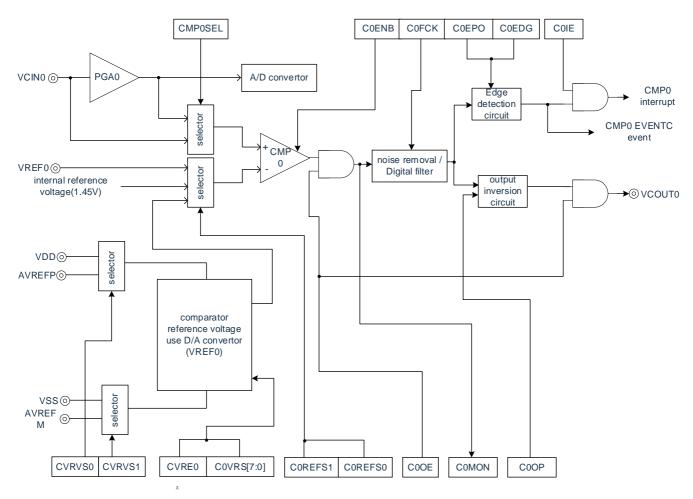

| Chapter 12 Comparator                                                       | 283 |

| 12.1 Function of comparator                                                 |     |

| 12.2 Structure of comparator                                                |     |

| 12.3 Registers for controlling comparator                                   |     |

| 12.3.1 Peripheral enable register 1 (PER1)                                  |     |

| 12.3.2 Comparator mode configuration register (COMPMDR)                     |     |

| 12.3.3 Comparator filter control register (COMPFIR)                         |     |

| 12.3.4 Comparator output control register (COMPOCR)                         | 291 |

| 12.3.5 Comparator built-in reference voltage control register (CVRCTL)      | 293 |

| 12.3.6 Comparator built-in reference voltage selection register (CiRVM)     | 294 |

| 12.3.7 Comparator 0 input signal selection control register (CMPSEL0)       | 295 |

| 12.3.8 Comparator 1 input signal selection control register (CMPSEL1)       | 296 |

| 12.3.9 Comparator 0 hysteresis control register (CMP0HY)                    | 297 |

| 12.3.10 Comparator 1 hysteresis control register (CMP1HY)                   | 298 |

| 12.3.11 Registers for controlling analog input pin port function            | 299 |

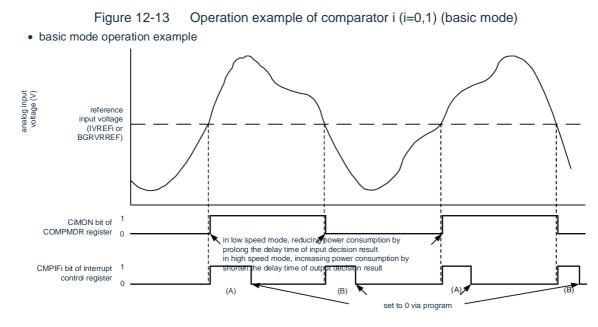

| 12.4 Operation Instructions                                                 |     |

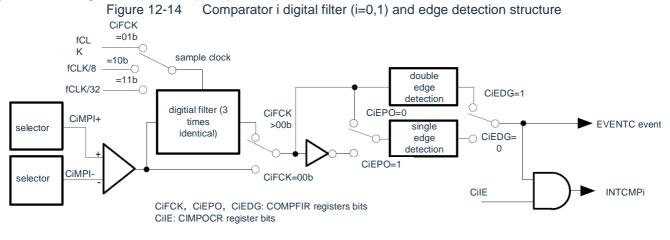

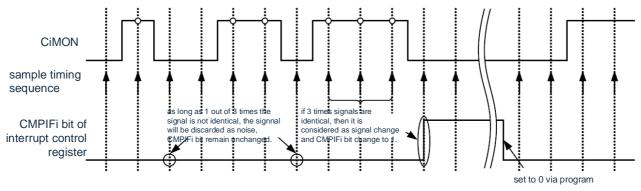

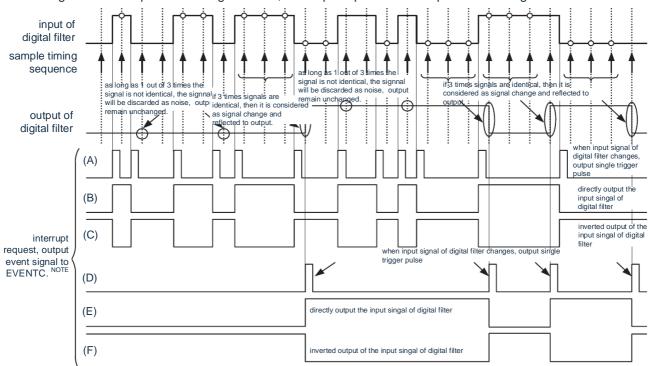

| 12.4.1 Digital filter of comparator i (i=0,1)                               |     |

| 12.4.2 Comparator i interrupts (i=0,1)                                      |     |

| 12.4.3 Event signals output to the linkage controller (EVENTC)              |     |

| 12.4.4 Output of comparator i (i=0,1)                                       |     |

| 12.4.5 Stop and supply of comparator clock                                  |     |

| Chapter 13 Programmable Gain Amplifier (PGA)                                | 305 |

| 13.1 Function of programmable gain amplifier                                | 305 |

| 13.2 Registers for programmable gain amplifier                              | 306 |

| 13.2.1 Peripheral enable register 1 (PER1)                                  | 306 |

| 13.2.2 Programmable gain amplifier control register (PGAnCTL)               |     |

|                                                                             |     |

| 13.2.3 Programmable gain amplifier sample hold control register (PGA0SH)       |     |

|--------------------------------------------------------------------------------|-----|

| 13.2.4 Registers for controlling analog input pin port function                |     |

| 13.3 Operation of programmable gain amplifier                                  |     |

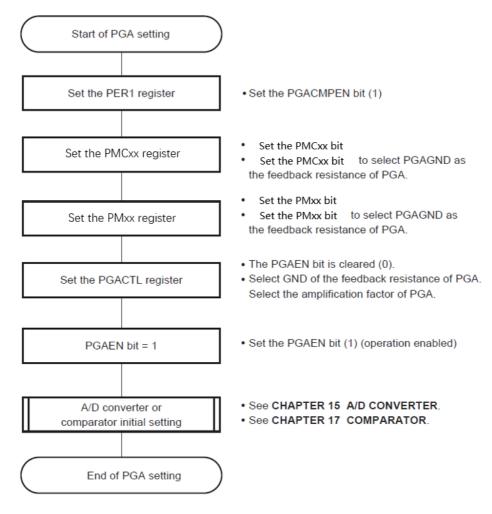

| 13.3.1 Starting operation steps of programmable gain amplifier                 |     |

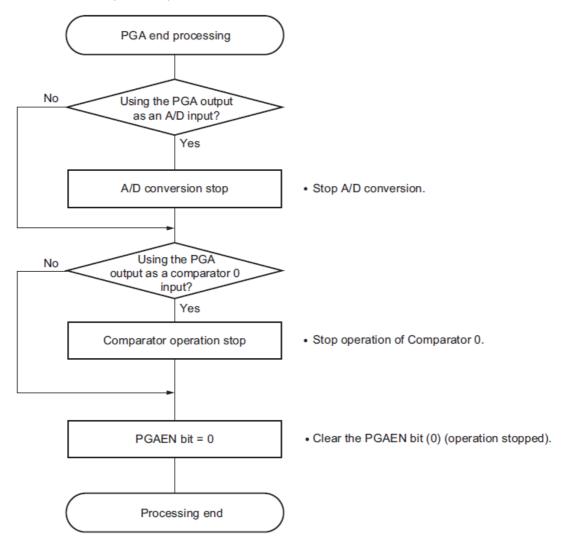

| 13.3.2 Stopping operation steps of programmable gain amplifier                 | 310 |

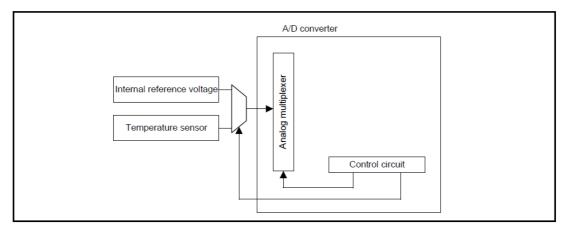

| Chapter 14 A/D Converter                                                       |     |

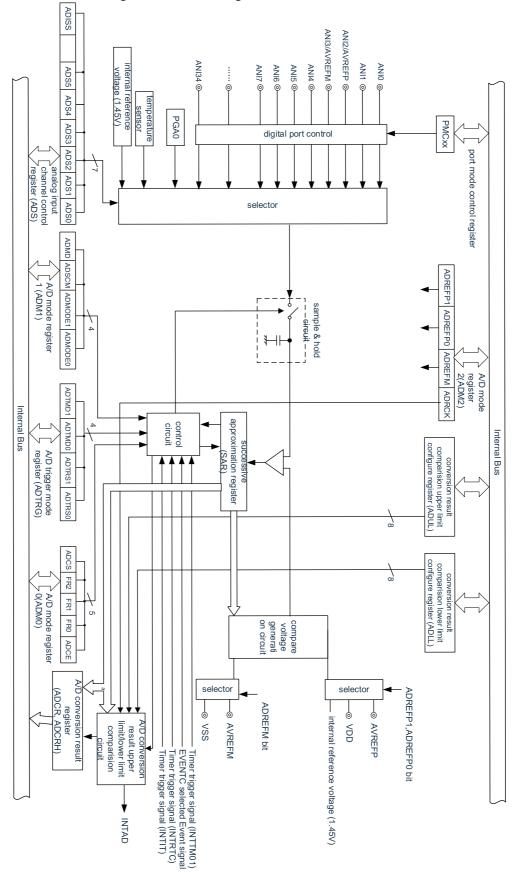

| 14.1 Function of A/D converter                                                 | 311 |

| 14.2 Registers for controlling A/D converter                                   |     |

| 14.2.1 Peripheral enable register 0 (PER0)                                     | 314 |

| 14.2.2 A/D converter mode register 0 (ADM0)                                    | 315 |

| 14.2.3 A/D converter mode register 1 (ADM1)                                    |     |

| 14.2.4 A/D converter mode register 2 (ADM2)                                    |     |

| 14.2.5 A/D converter trigger mode register (ADTRG)                             |     |

| 14.2.6 Analog input channel specification register (ADS)                       |     |

| 14.2.7 12-bit A/D conversion result register (ADCR)                            |     |

| 14.2.8 8-bit A/D conversion result register (ADCRH)                            |     |

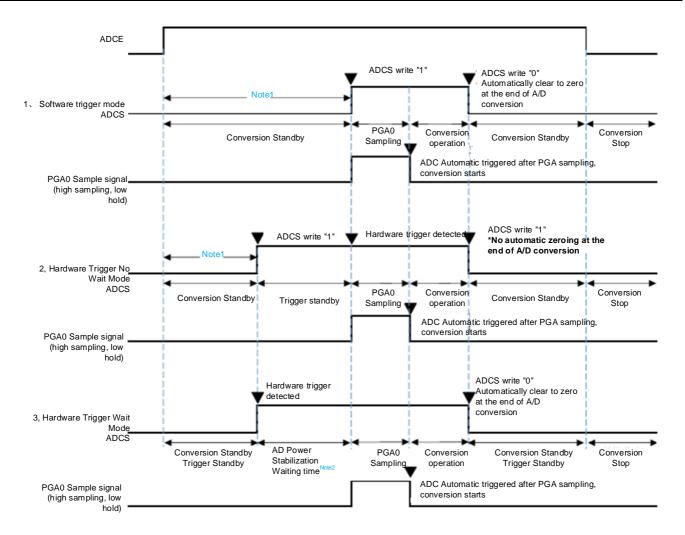

| 14.2.9 Conversion result comparison lower limit setting register (ADUL)        |     |

| 14.2.10 Conversion result comparison lower limit setting register (ADLL)       |     |

| 14.2.11 A/D converter sampling time control register (ADNSMP)                  |     |

| 14.2.12 A/D sample time extension register (ADSMPWAIT)                         |     |

| 14.2.13 A/D test register (ADTES)                                              |     |

| 14.2.14 A/D status register (ADFLG)                                            |     |

| 14.2.15 A/D charge/discharge control register (ADNDIS)                         |     |

| 14.2.16 Programmable gain amplifier sample and hold control register (PGA0SH)  |     |

| 14.2.17 Registers for controlling analog input pin port function               |     |

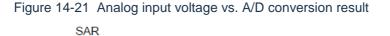

| 14.3 Input voltage and conversion results                                      |     |

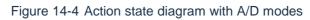

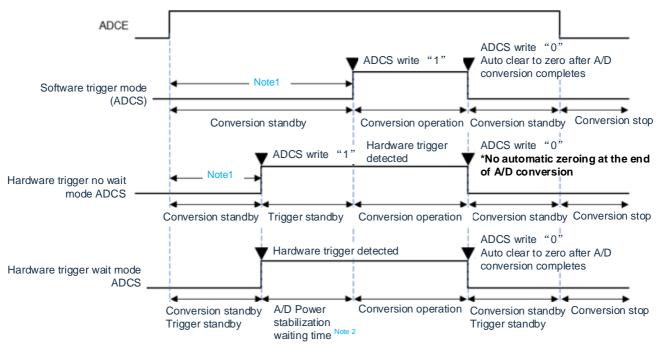

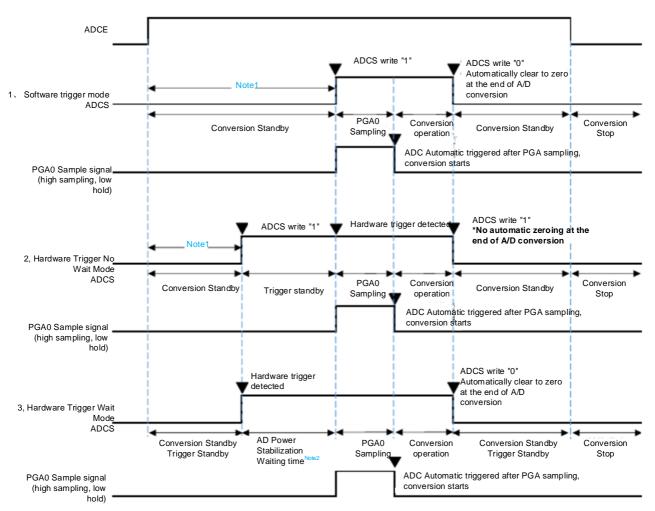

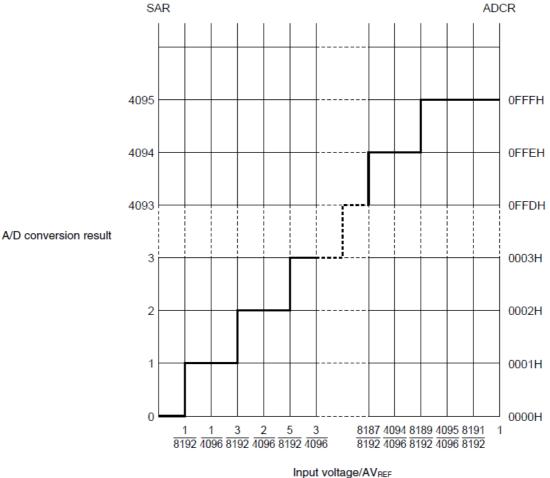

| 14.4 Operation mode of A/D converter                                           |     |

| 14.4.1 Software trigger mode (select mode, continuous conversion mode)         |     |

| 14.4.2 Software trigger mode (select mode, single conversion mode)             | 341 |

| 14.4.3 Software trigger mode (scan mode, continuous conversion mode)           |     |

| 14.4.4 Software trigger mode (scan mode, single conversion mode)               |     |

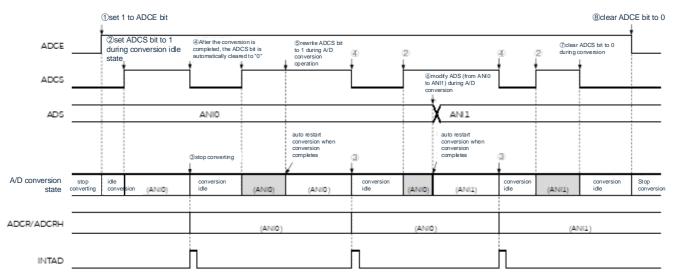

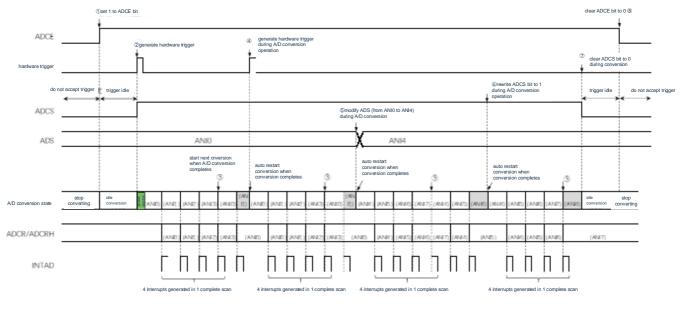

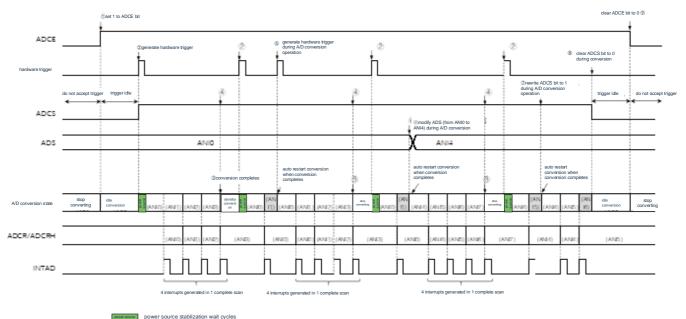

| 14.4.5 Hardware trigger no-wait mode (select mode, continuous conversion mode) |     |

| 14.4.6 Hardware trigger no-wait mode (select mode, single conversion mode)     | 345 |

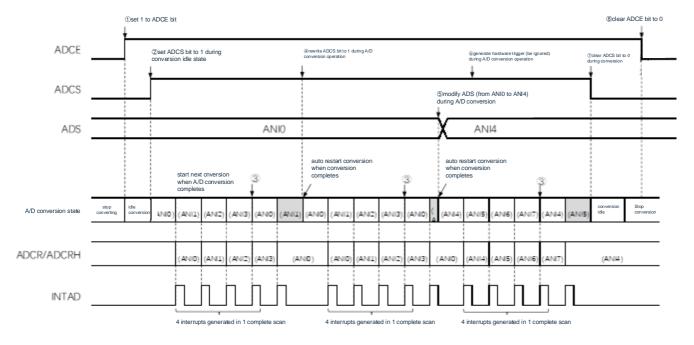

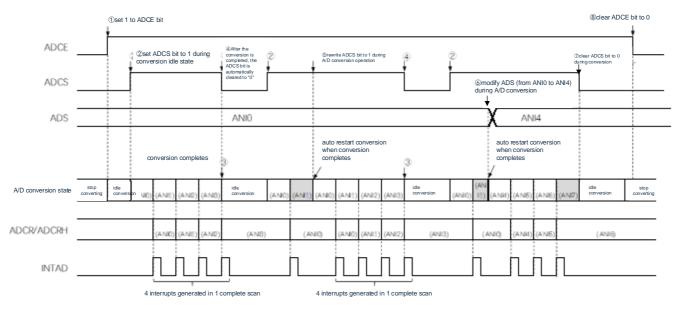

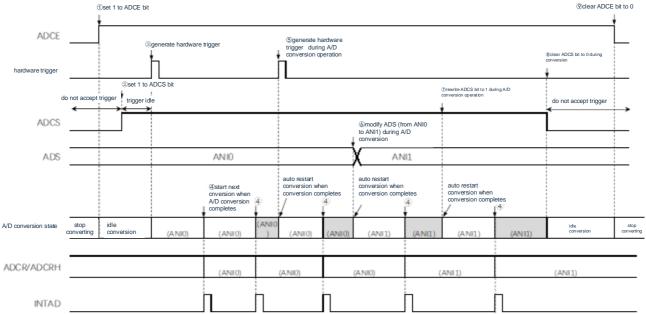

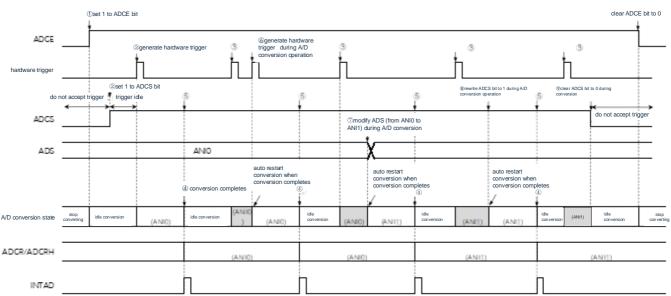

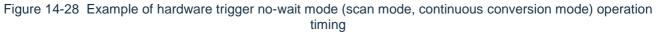

| 14.4.7 Hardware trigger no-wait mode (scan mode, continuous conversion mode)   | 346 |

| 14.4.8 Hardware trigger no-wait mode (scan mode, single conversion mode)       |     |

| 14.4.9 Hardware trigger wait mode (select mode, continuous conversion mode)    |     |

| 14.4.10 Hardware trigger wait mode (select mode, single conversion mode)       |     |

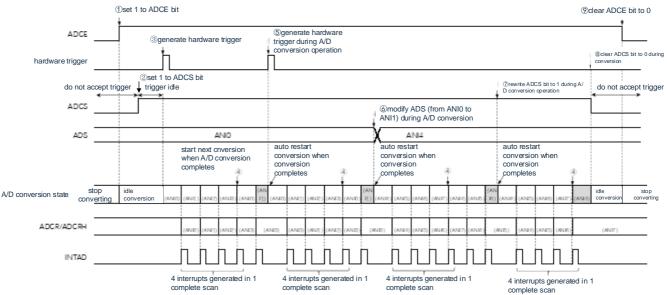

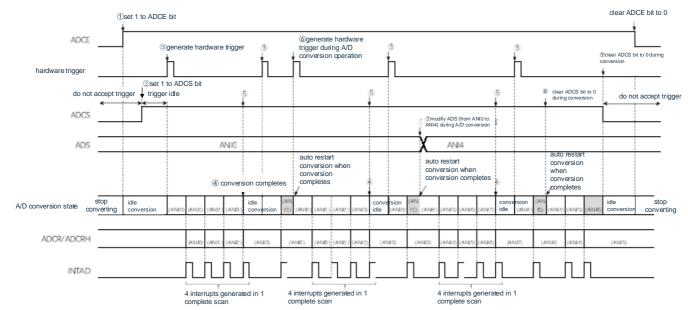

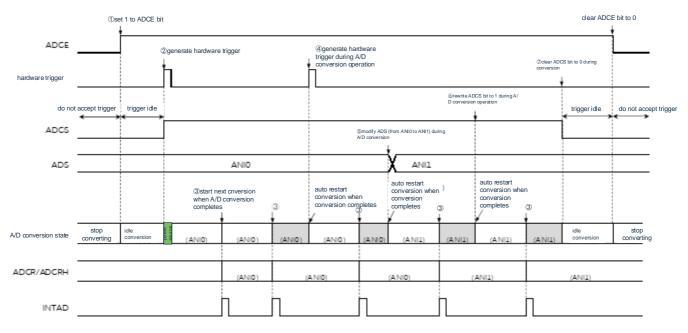

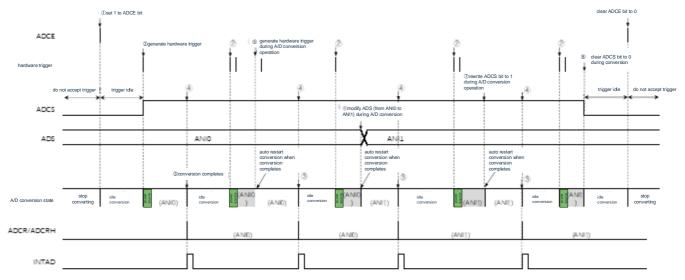

| 14.4.11 Hardware trigger wait mode (scan mode, continuous conversion mode)     | 350 |

| 14.4.12 Hardware trigger wait mode (scan mode, single conversion mode)         | 351 |

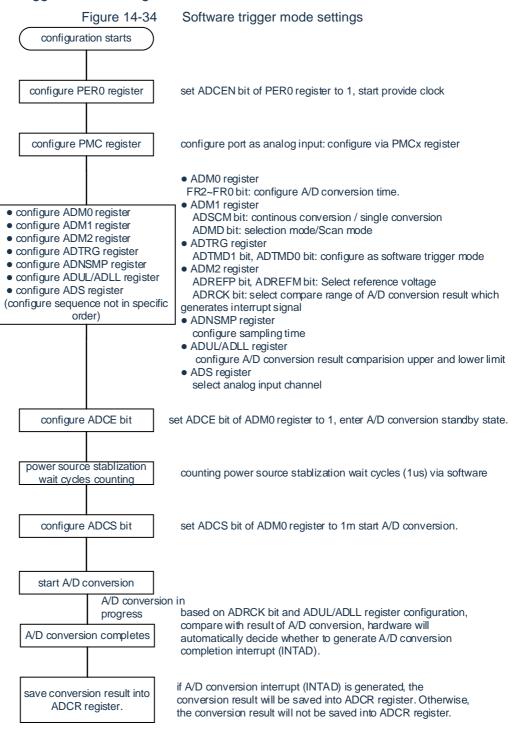

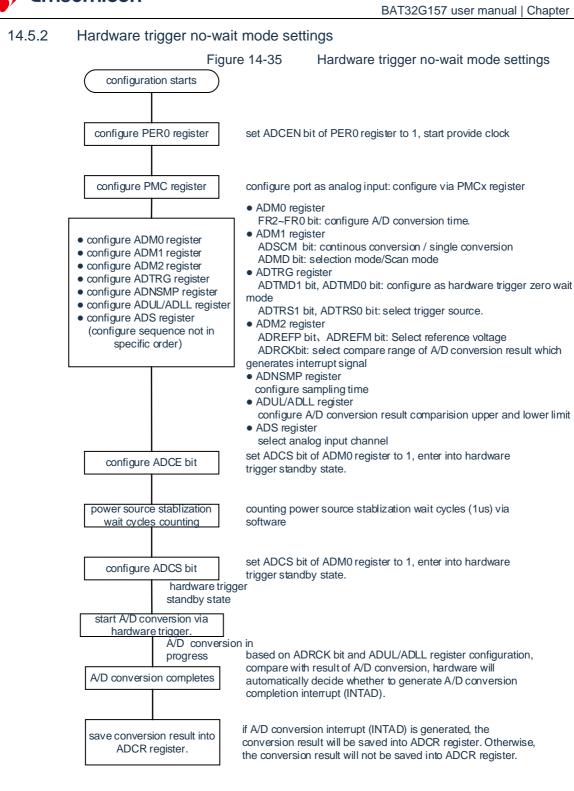

| 14.5 A/D converter set-up flowchart                                            |     |

| 14.5.1 S    | Software trigger mode settings                                                             | 352    |

|-------------|--------------------------------------------------------------------------------------------|--------|

| 14.5.2 H    | lardware trigger no-wait mode settings                                                     | 353    |

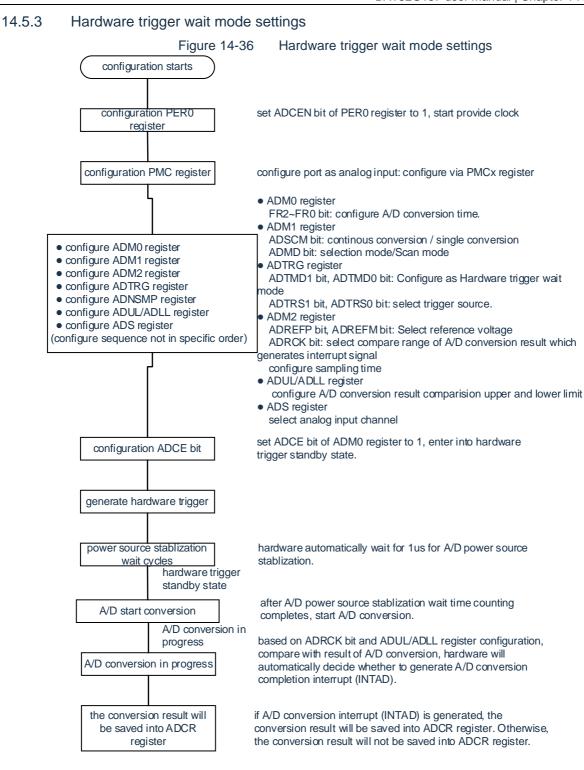

| 14.5.3 H    | lardware trigger wait mode settings                                                        | 354    |

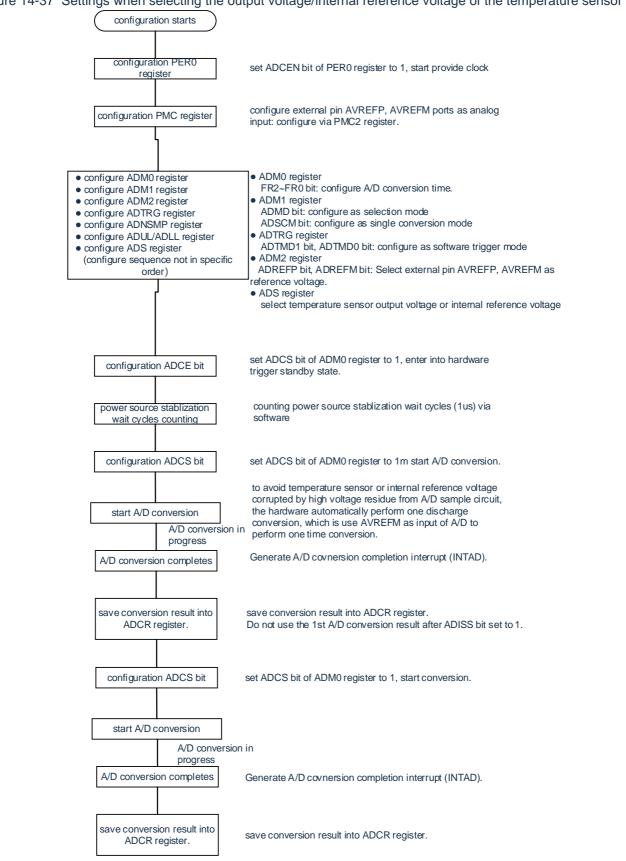

| 14.5.4 S    | Settings when selecting the output voltage/internal reference voltage of temperaturesensor | 355    |

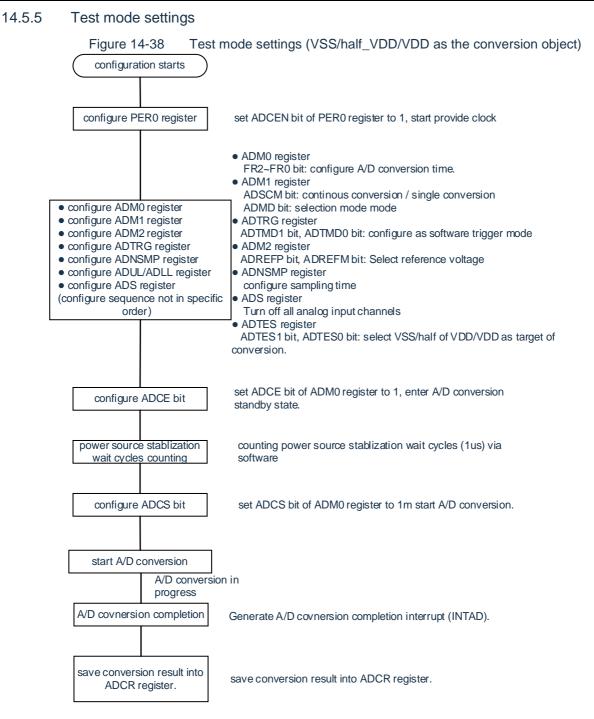

| 14.5.5 T    | est mode settings                                                                          | 356    |

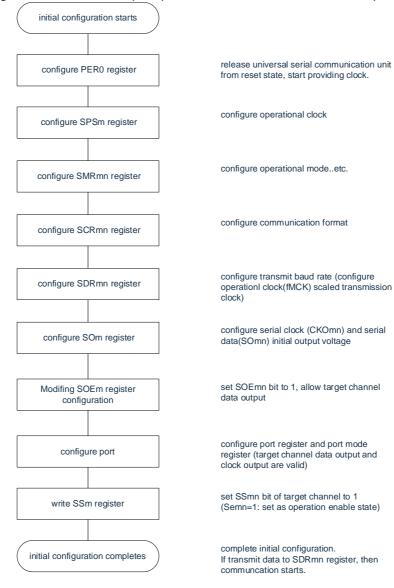

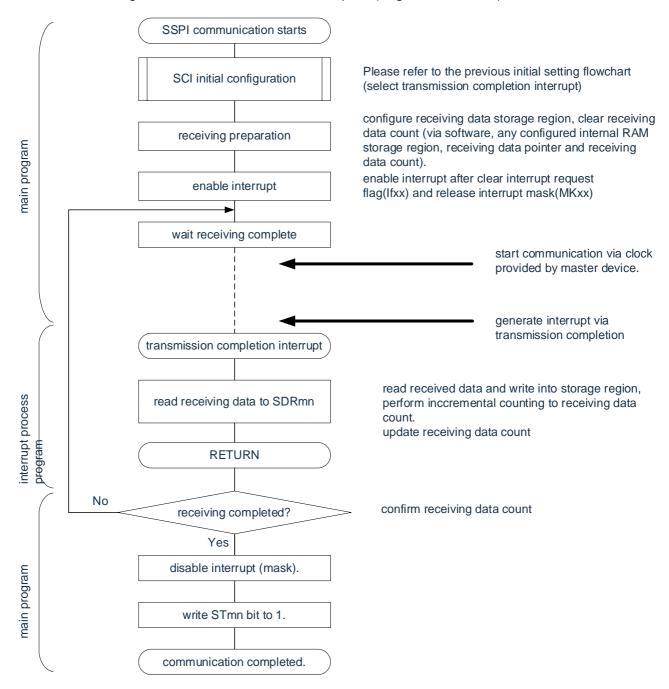

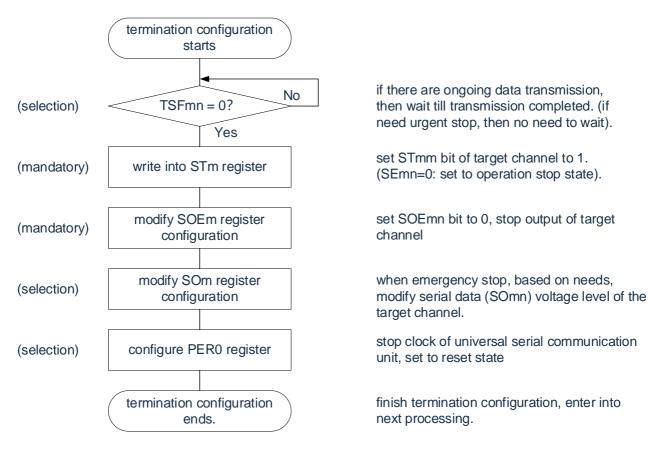

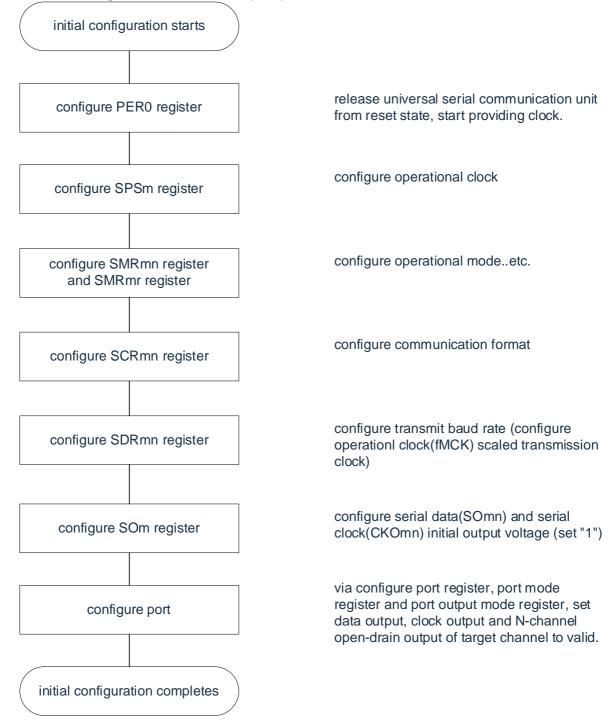

| Chapter 1   | 5 Universal Serial Communication Unit                                                      | 357    |

| 15.1 Fun    | ction of universal serial communication unit                                               | 358    |

| 15.1.1 3    | -wire serial I/O (SSPI00, SSPI01, SSPI10, SSPI11, SSPI20,SSPI21)                           | 358    |

| 15.1.2 L    | JART (UART0~UART2)                                                                         | 359    |

| 15.1.3 S    | Simplified I2C (IIC00, IIC01, IIC10, IIC11, IIC20,IIC21)                                   | 360    |

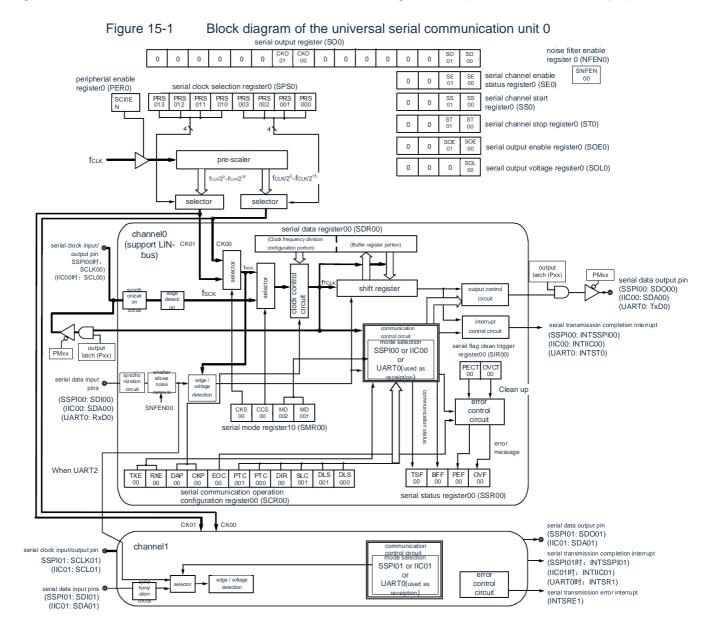

| 15.2 Stru   | acture of universal serial communication unit                                              | 361    |

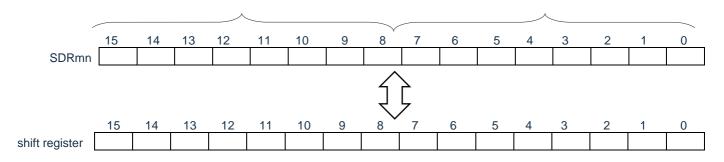

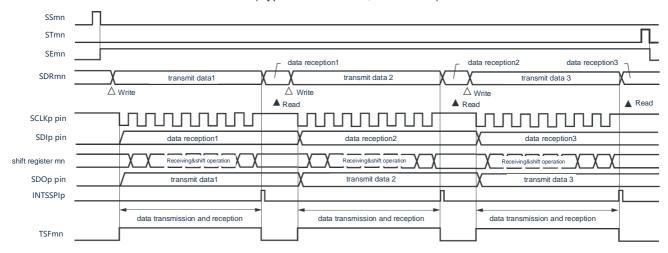

| 15.2.1 S    | Shift register                                                                             | 363    |

| 15.2.2 S    | Serial data register mn (SDRmn)                                                            | 363    |

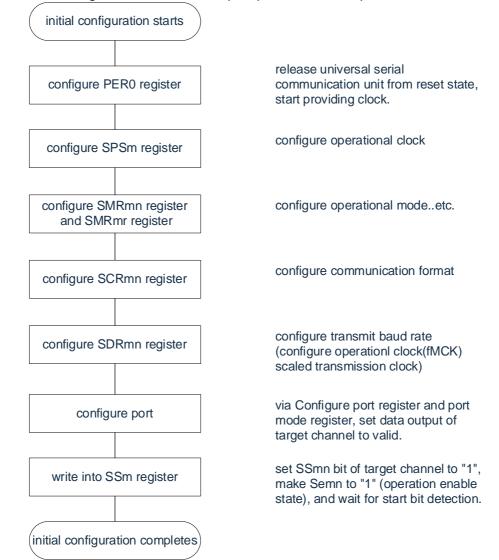

| 15.3 Reg    | gisters for controlling universal serial communication unit                                | 365    |

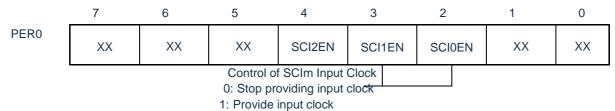

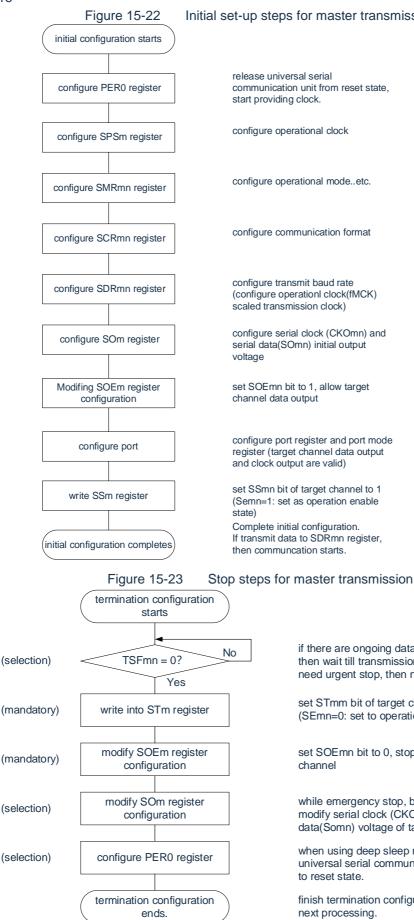

| 15.3.1 F    | Peripheral enable register 0 (PER0)                                                        | 367    |

| 15.3.2 S    | Serial clock select register m (SPSm)                                                      | 368    |

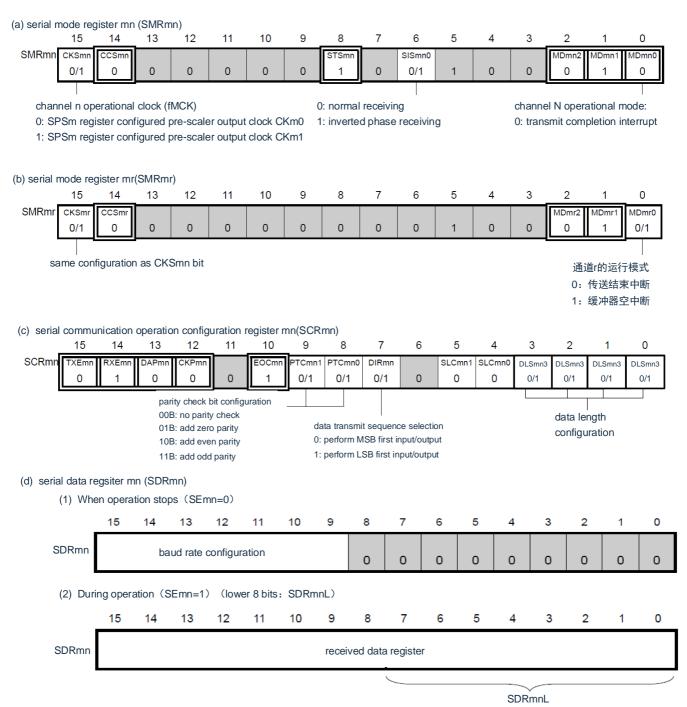

| 15.3.3 S    | Serial mode register mn (SMRmn)                                                            | 369    |

| 15.3.4 S    | Serial communication run setting register mn (SCRmn)                                       | 371    |

| 15.3.5 S    | Serial data register mn (SDRmn)                                                            | 374    |

| 15.3.6 S    | Serial flag clear trigger register mn (SIRmn)                                              | 375    |

| 15.3.7 S    | Serial status register mn (SSRmn)                                                          | 376    |

| 15.3.8 S    | Serial channel start register m (SSm)                                                      | 378    |

| 15.3.9 S    | Serial channel stop register m (STm)                                                       | 379    |

| 15.3.10 S   | Serial channel enable state register m (SEm)                                               | 380    |

| 15.3.11 S   | Serial output enable register m (SOEm)                                                     | 381    |

|             | Serial output register m (SOm)                                                             |        |

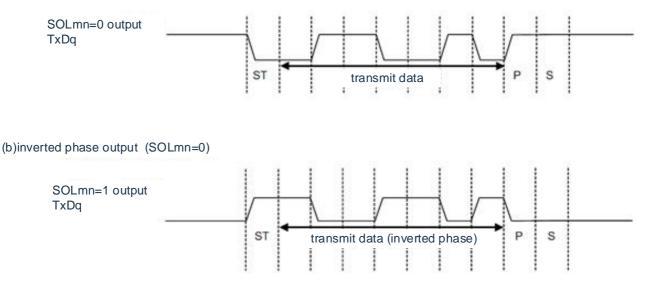

| 15.3.13 S   | Serial output level register m (SOLm)                                                      | 383    |

| 15.3.14 lr  | nput switch control register (ISC)                                                         | 384    |

| 15.3.15 N   | loise filter enable register 0 (NFEN0)                                                     | 385    |

| 15.3.16 F   | Registers for controlling serial input/output pin port                                     | 386    |

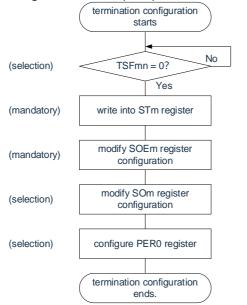

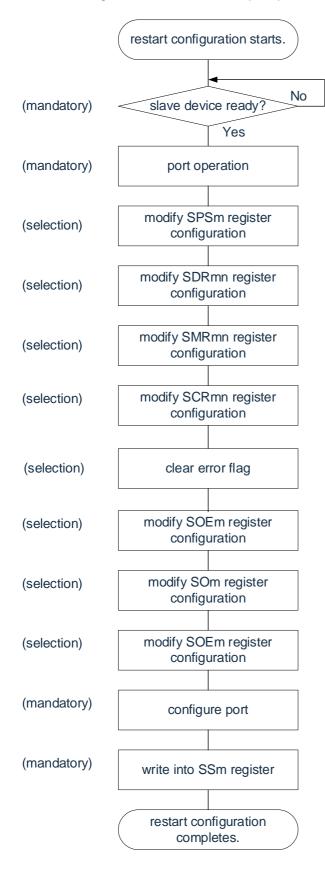

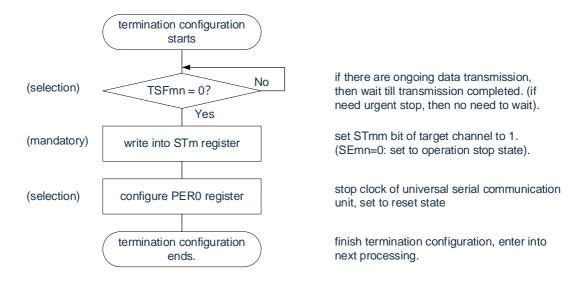

| 15.4 Rur    | n stop mode                                                                                | 387    |

| 15.4.1 S    | Stop operation by unit                                                                     | 387    |

| 15.4.2 S    | Stopping the operation by channels                                                         | 388    |

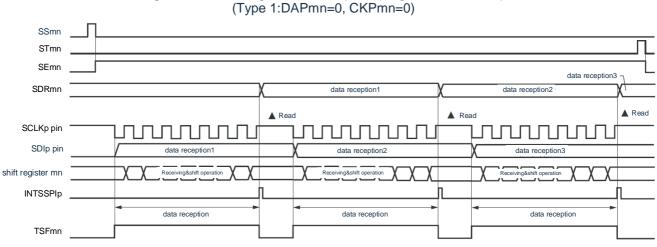

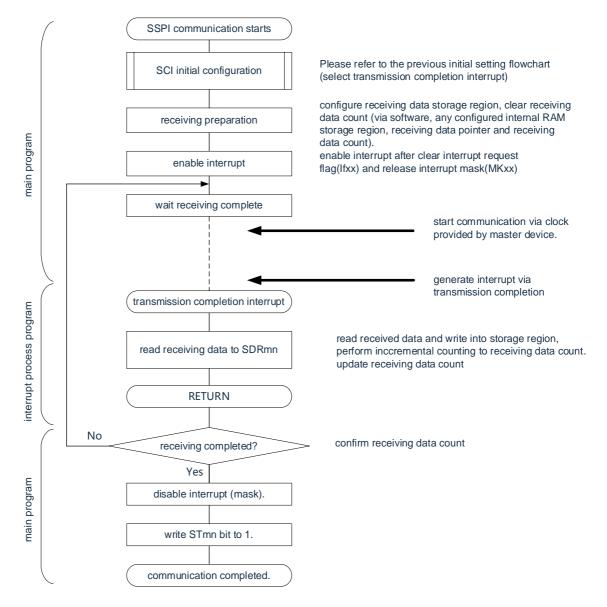

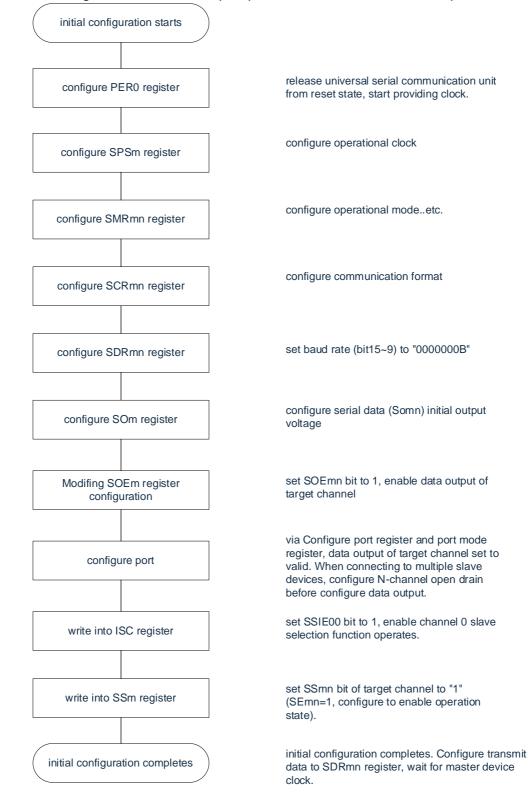

|             | ire serial I/O(SSPI00, SSPI01, SSPI10, SSPI11, SSPI20, SSPI21) communication               |        |

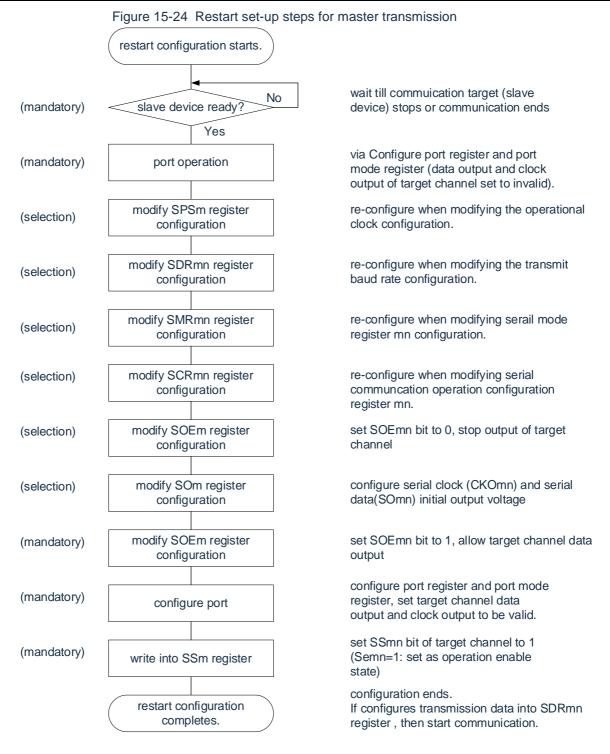

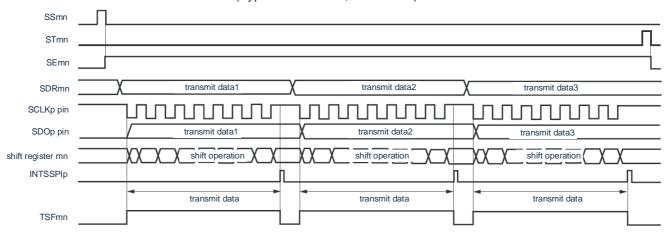

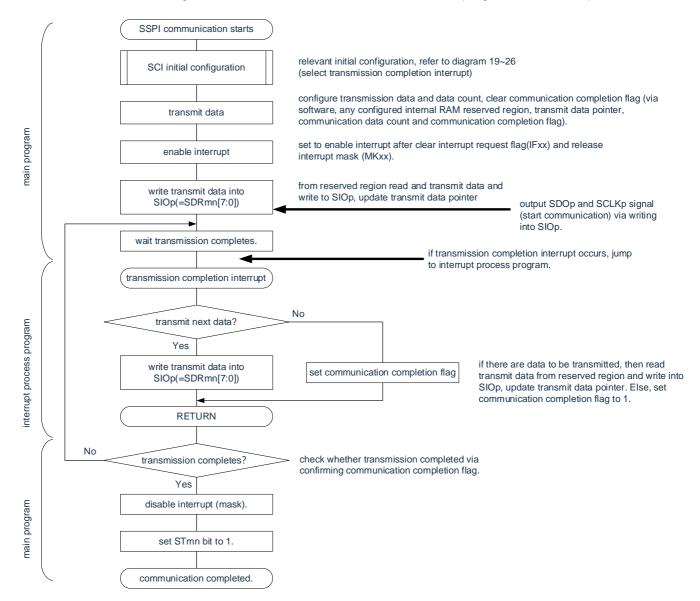

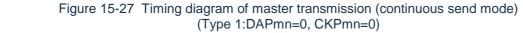

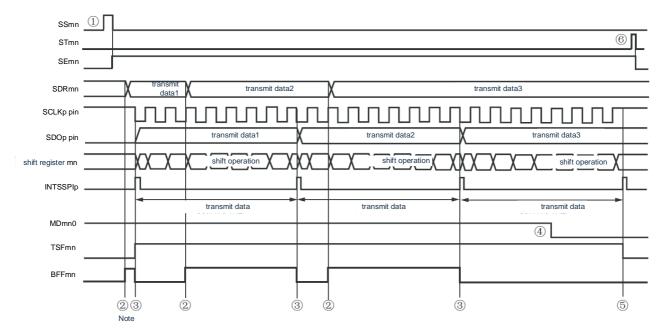

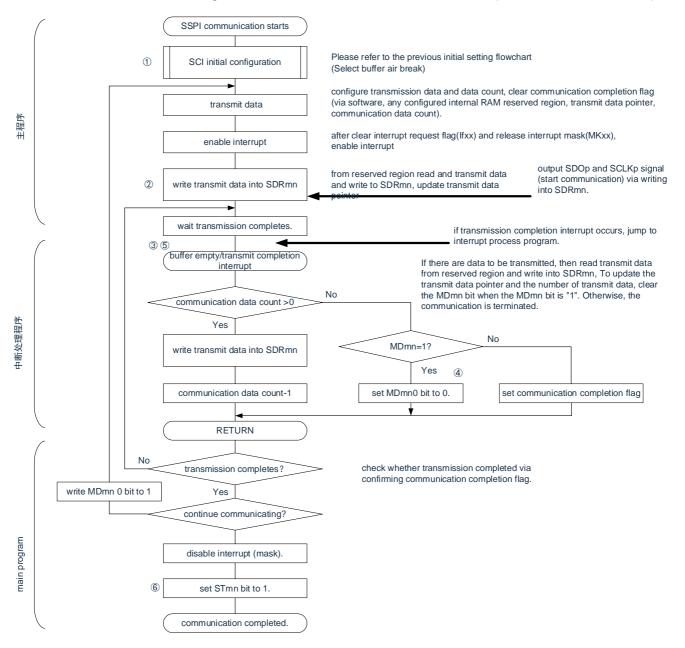

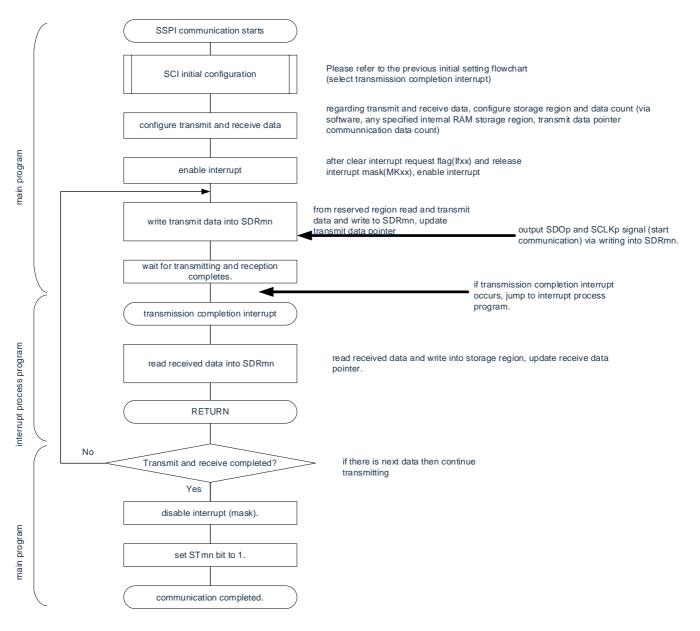

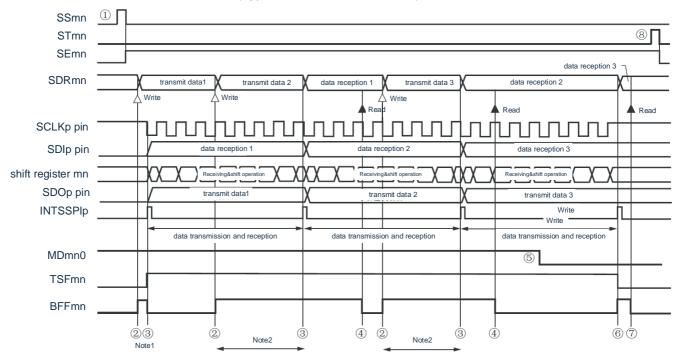

|             | Aaster transmission                                                                        |        |

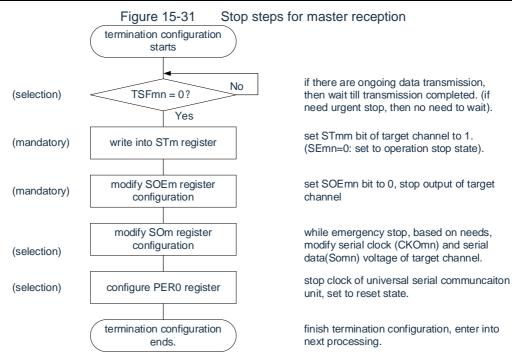

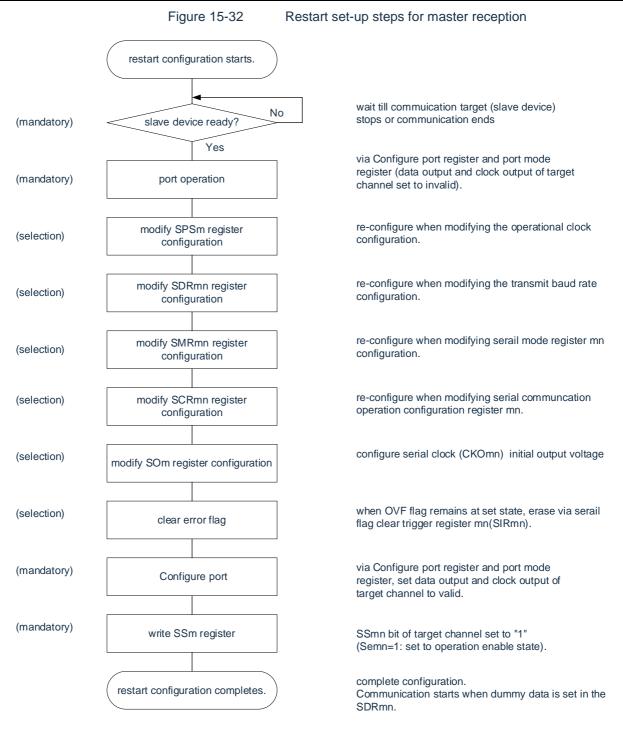

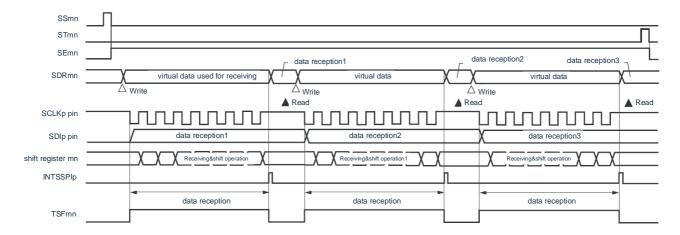

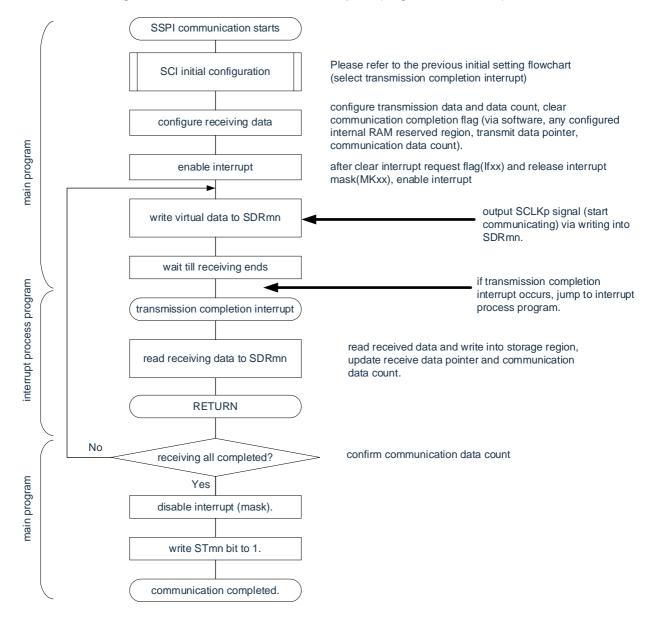

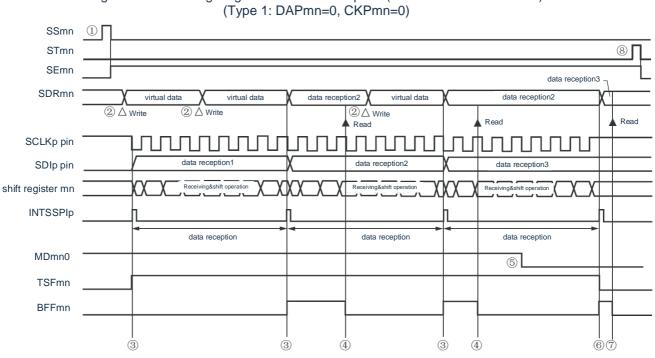

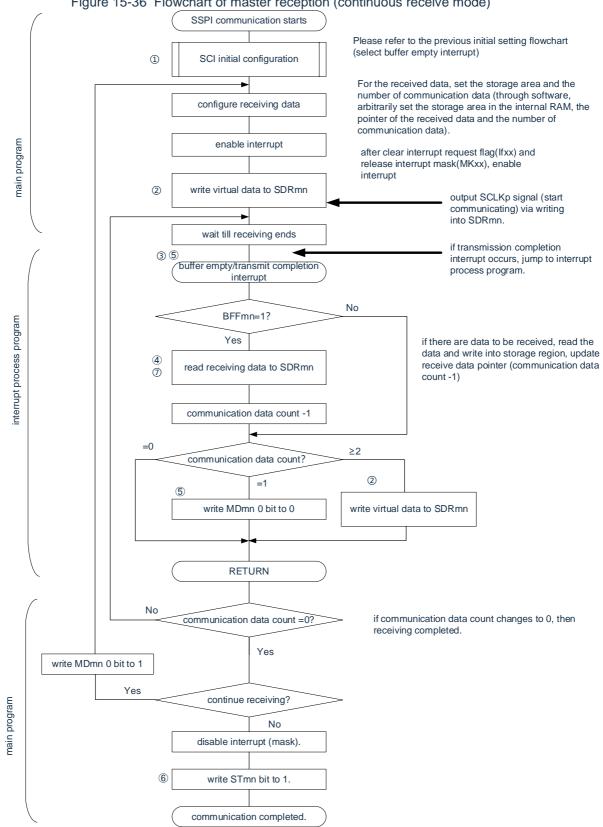

| 15.5.2 N    | Aaster reception                                                                           | 398    |

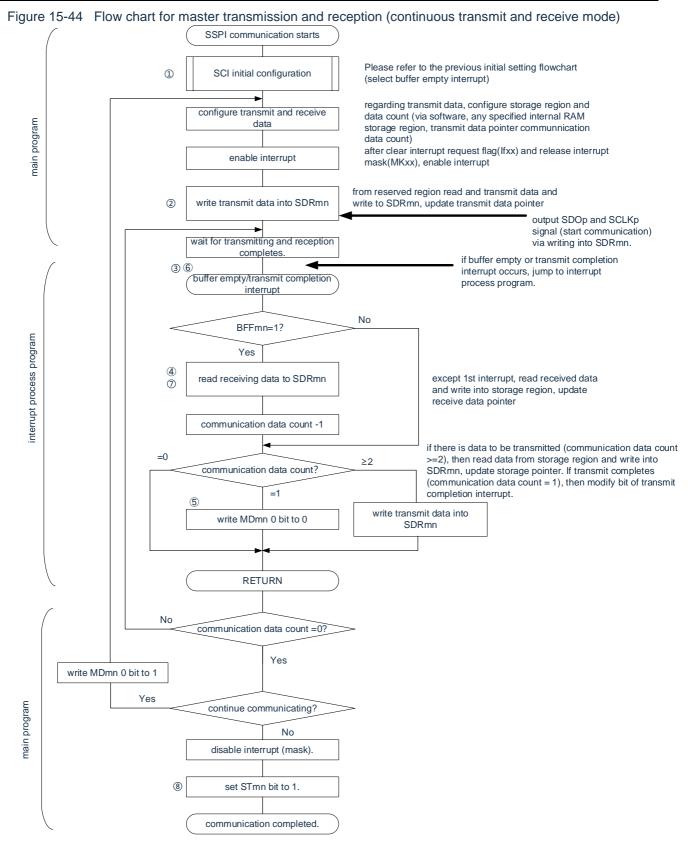

|             | Aaster transmission and reception                                                          |        |

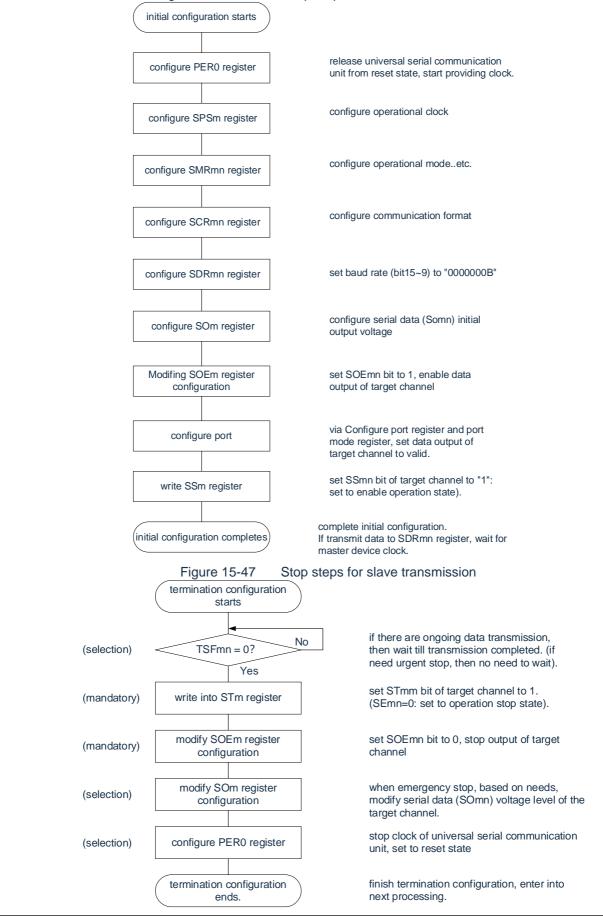

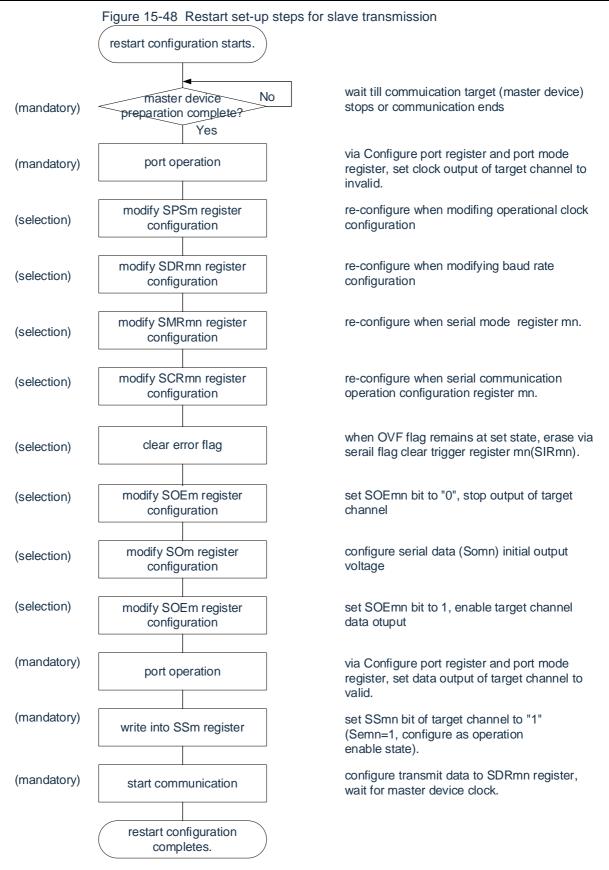

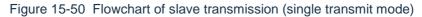

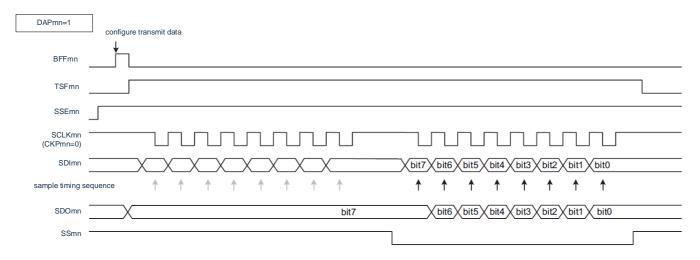

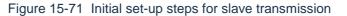

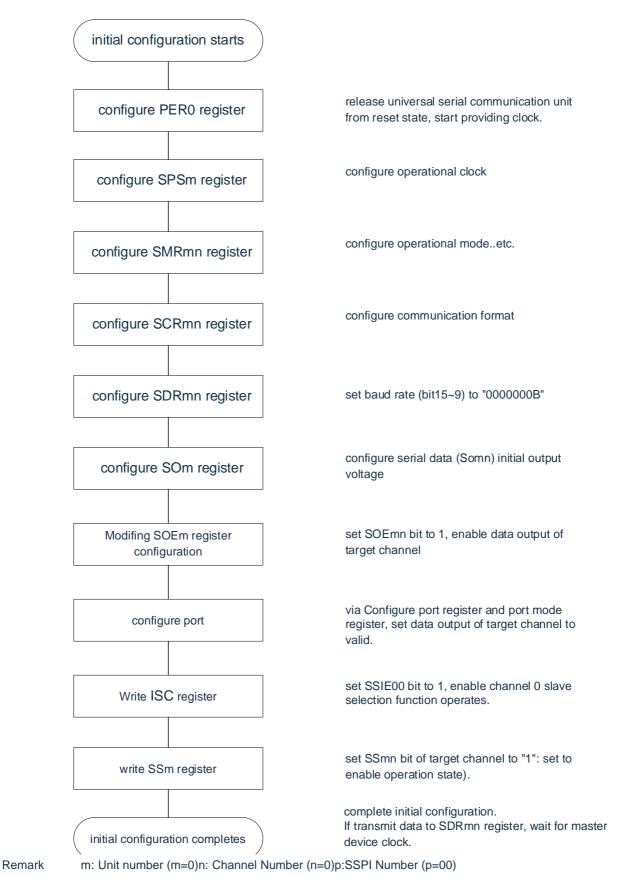

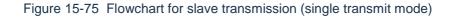

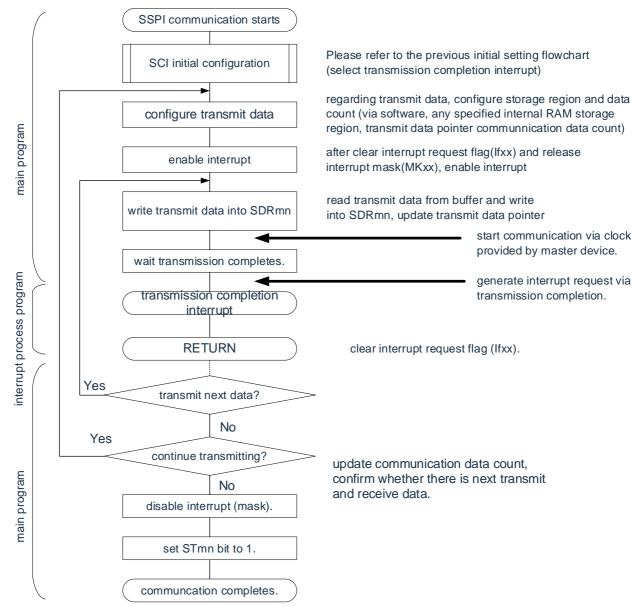

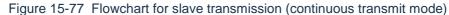

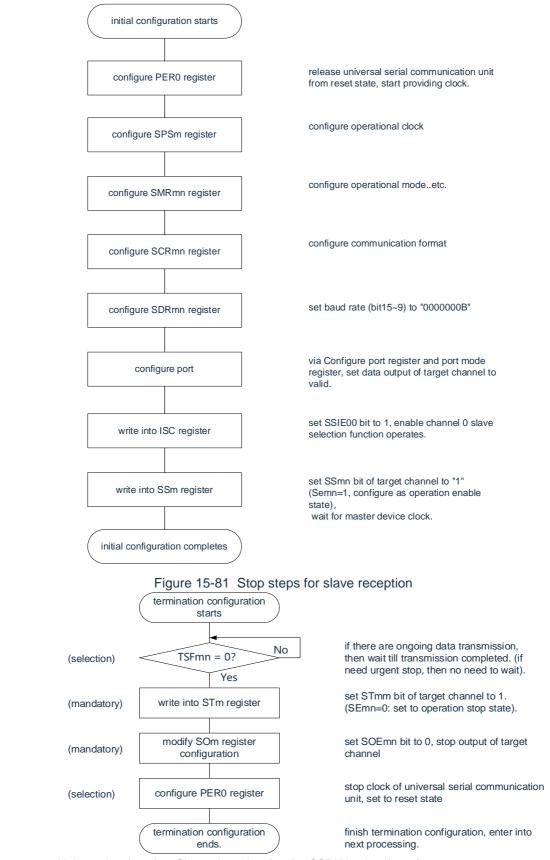

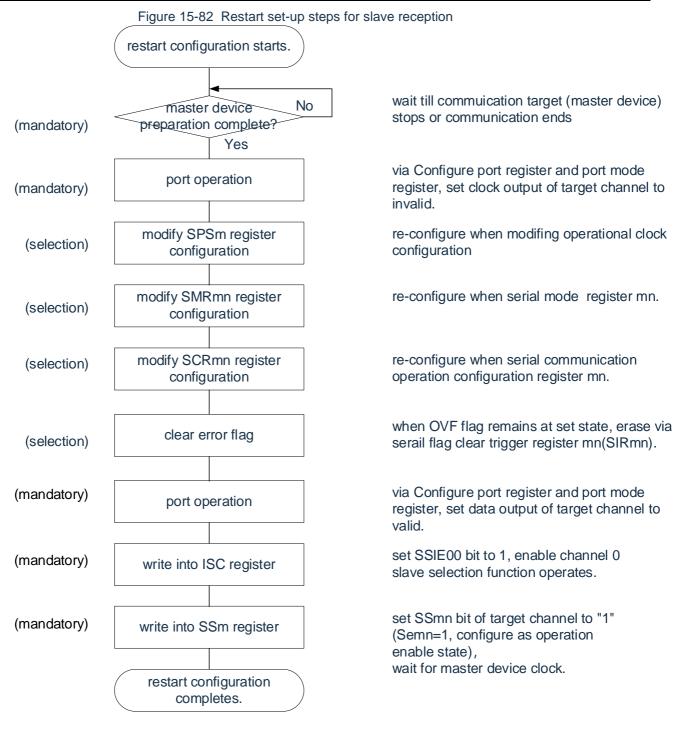

|             | Slave transmission                                                                         |        |

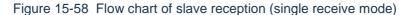

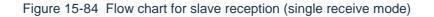

|             | Slave reception                                                                            |        |

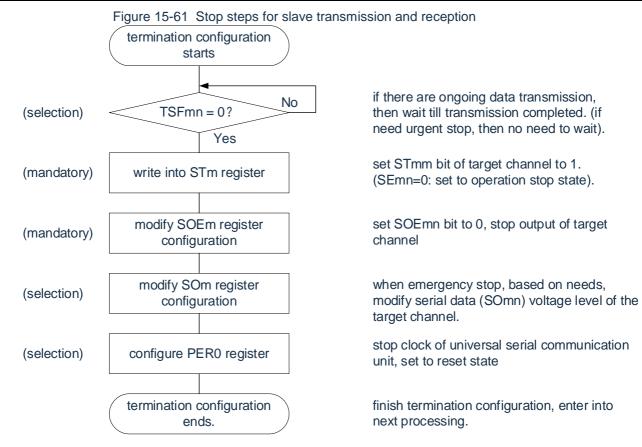

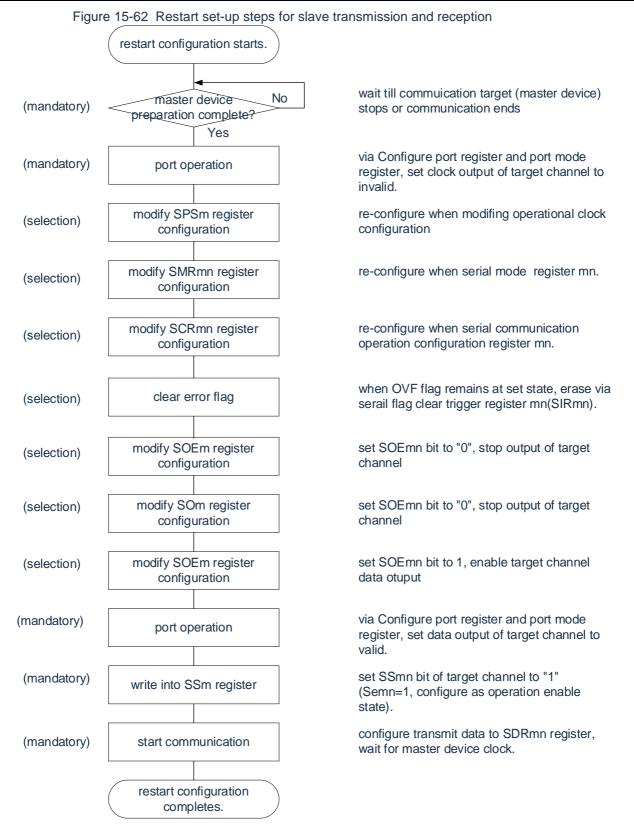

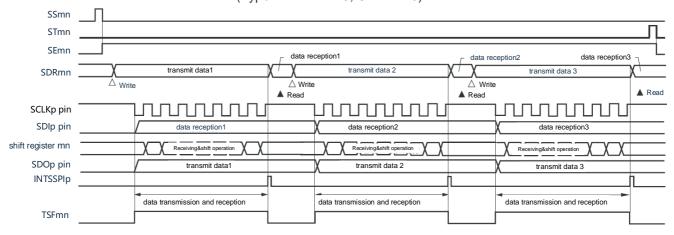

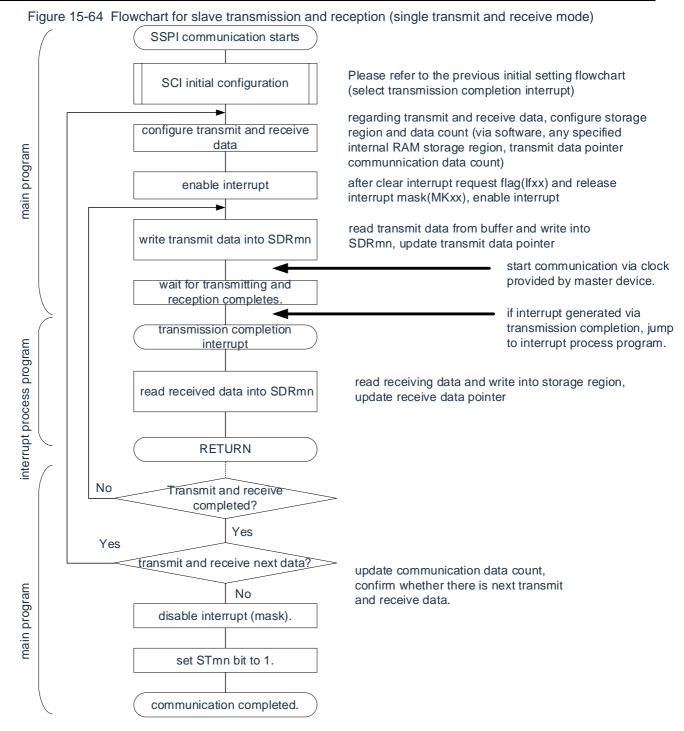

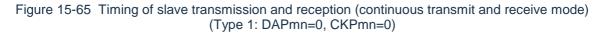

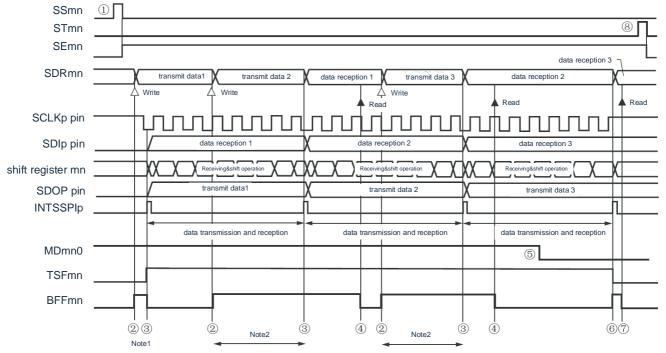

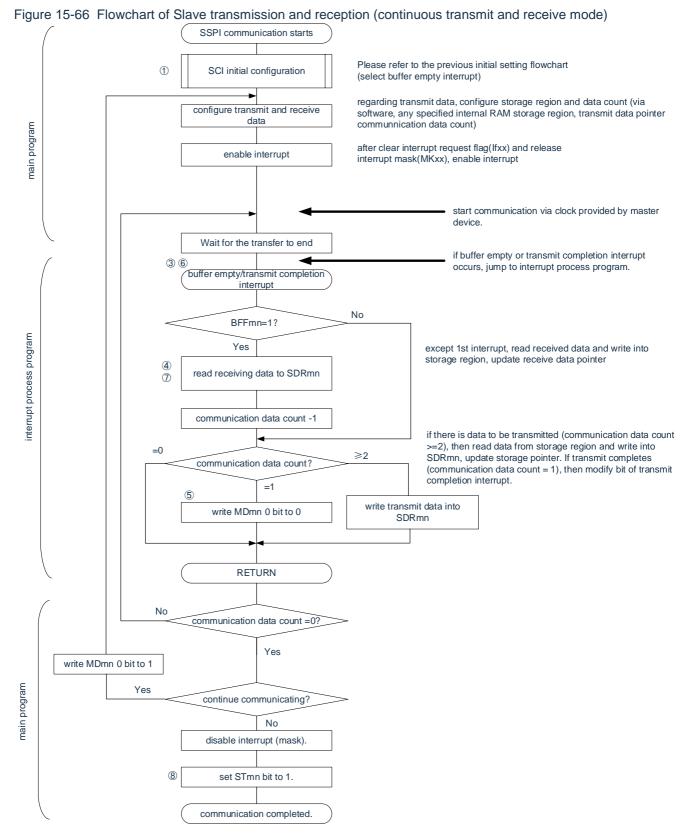

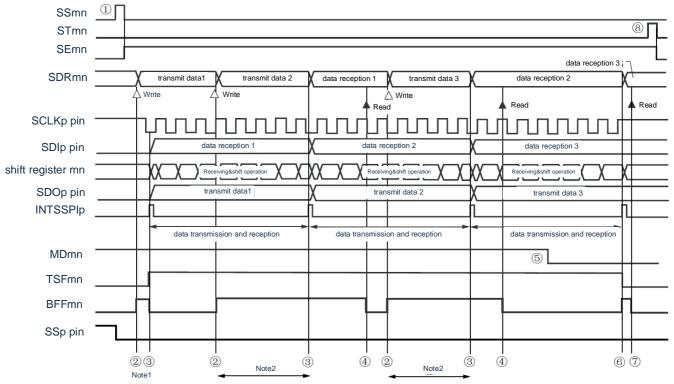

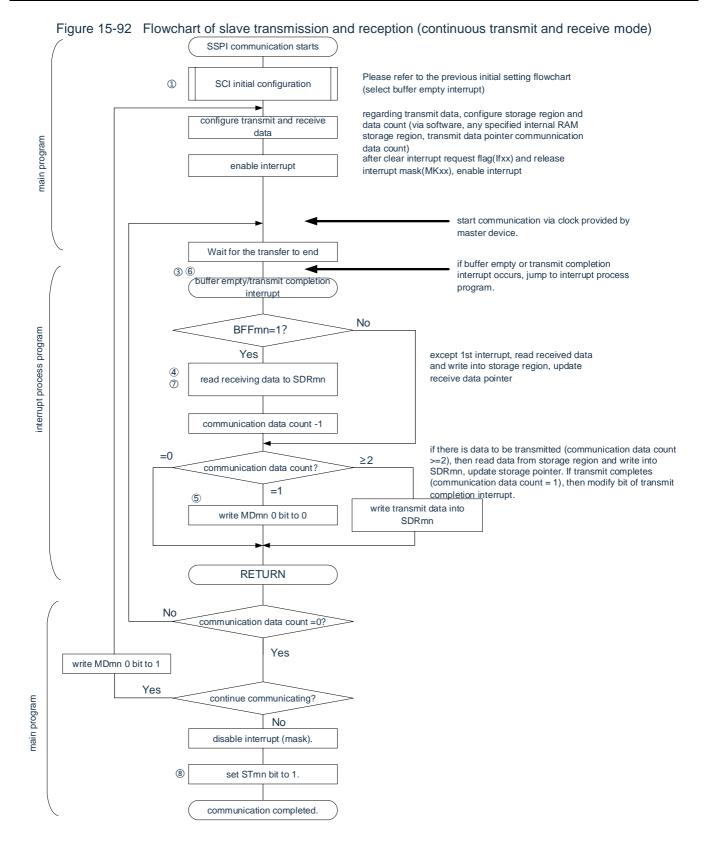

|             | Slave transmission and reception                                                           |        |

| www.mcu.com |                                                                                            | V1.0.5 |

| 15.5.7 Calculation of transmission clock frequency                                                                             | 439  |

|--------------------------------------------------------------------------------------------------------------------------------|------|

| 15.5.8 Procedure for errors occurring during 3-wire serial I/O communication (SSPI00, SSPI01, SSPI11, SSPI20, SSPI21)          |      |

| 15.6 Operation of clock-synchronous serial communication with slave select input function                                      | 442  |

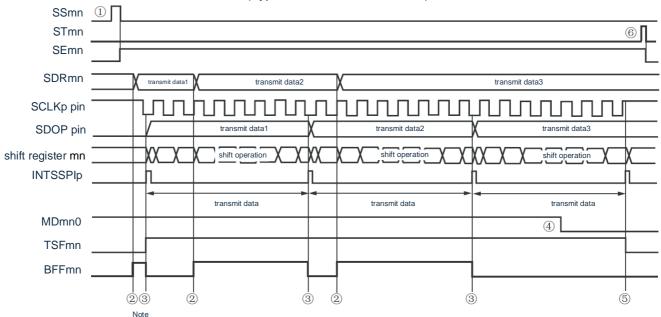

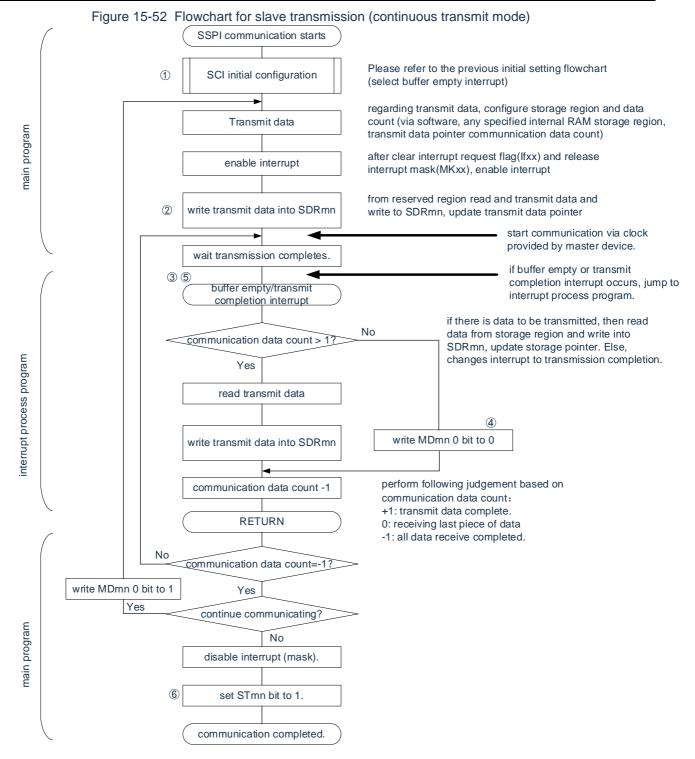

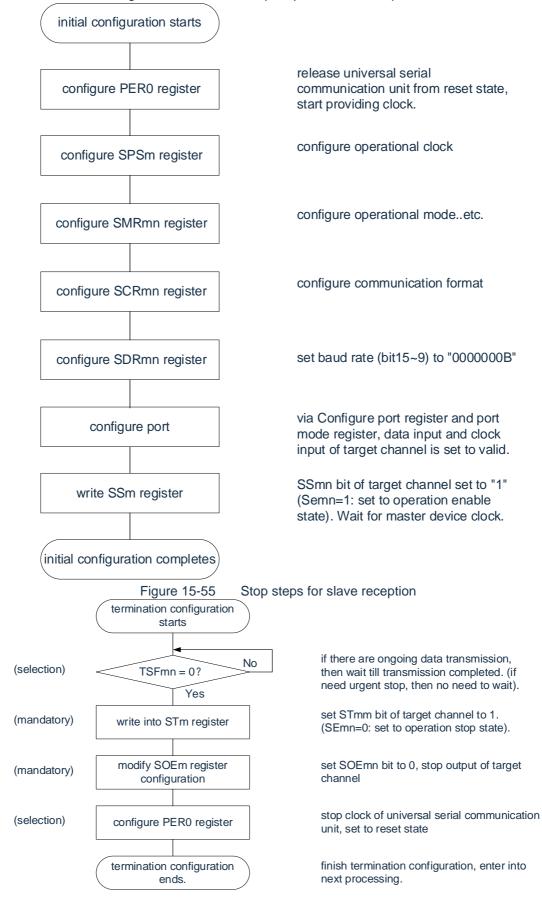

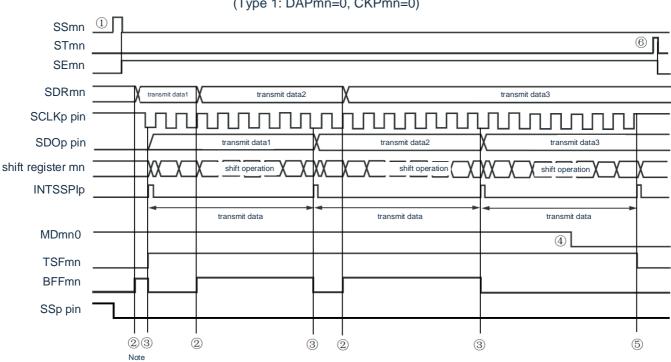

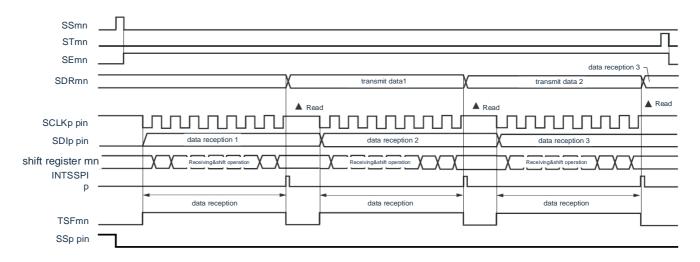

| 15.6.1 Slave transmission                                                                                                      |      |

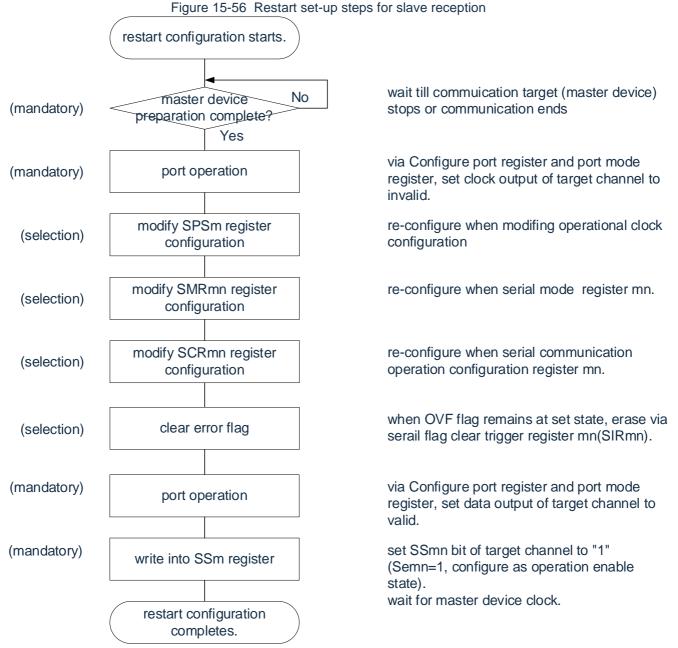

| 15.6.2 Slave reception                                                                                                         | 455  |

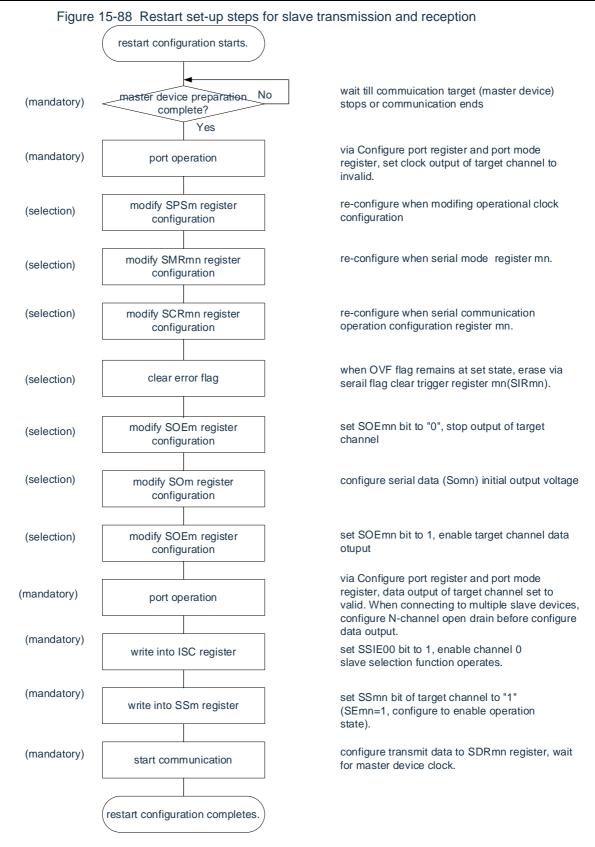

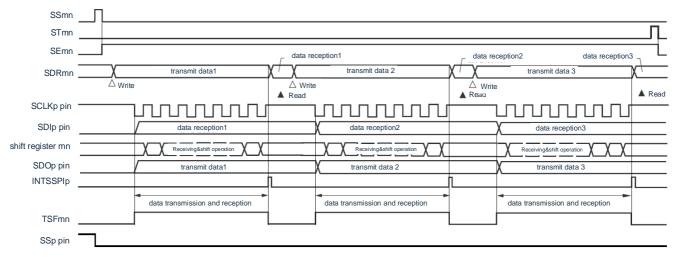

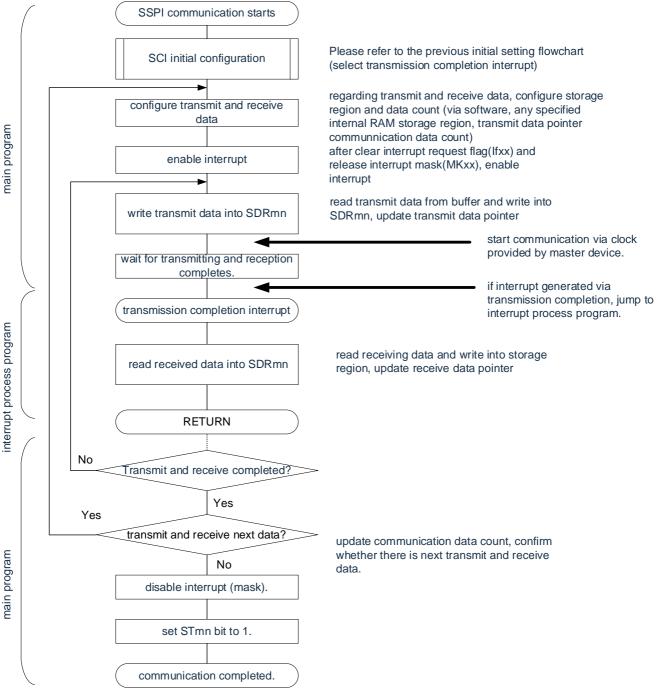

| 15.6.3 Slave transmission and reception                                                                                        |      |

| 15.6.4 Calculation of transmission clock frequency                                                                             | 472  |

| 15.6.5 Processing steps when an error occurs during clock sync serial communication of slave<br>input function                 |      |

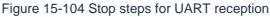

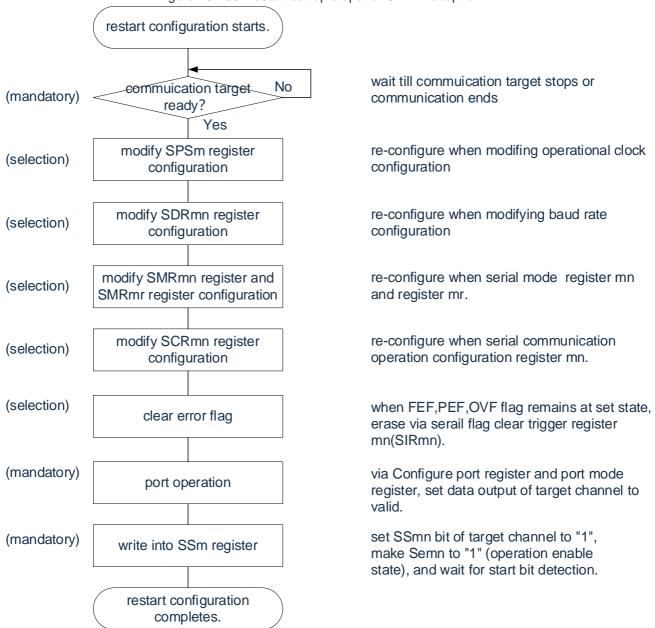

| 15.7 Operation of UART(UART0~UART2) communication                                                                              | 474  |

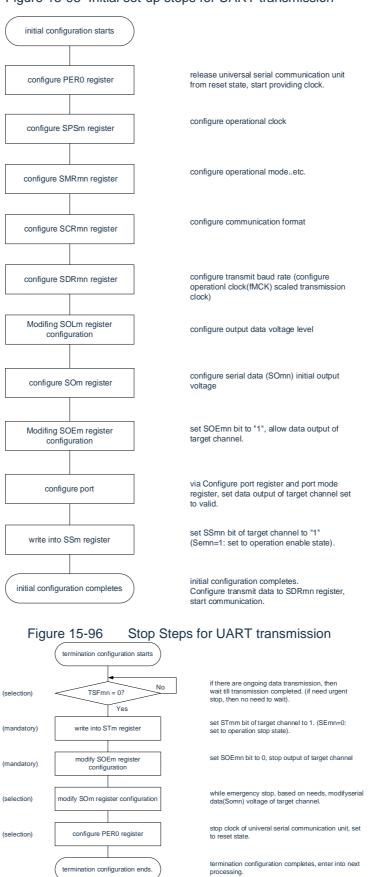

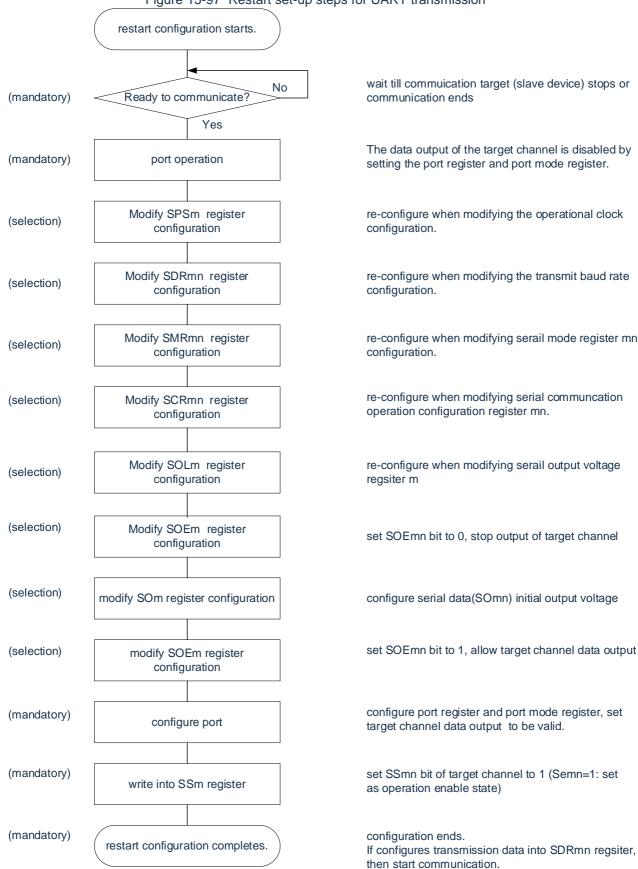

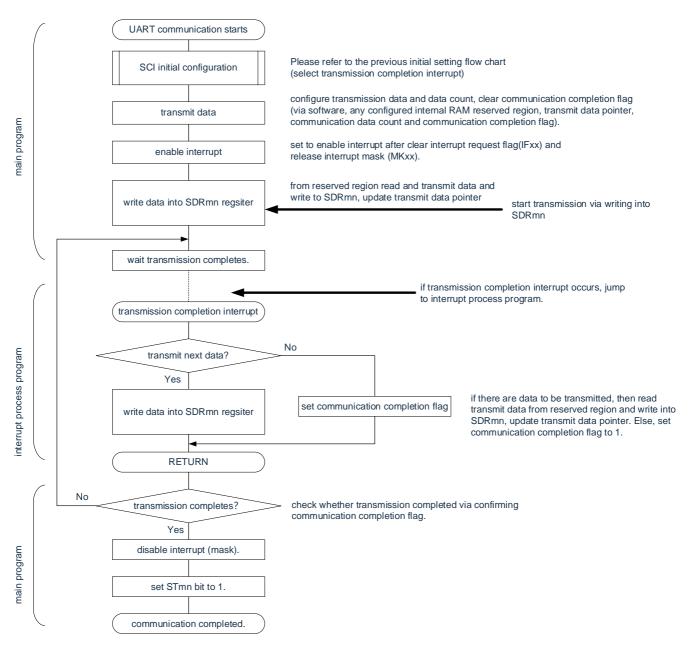

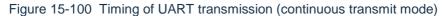

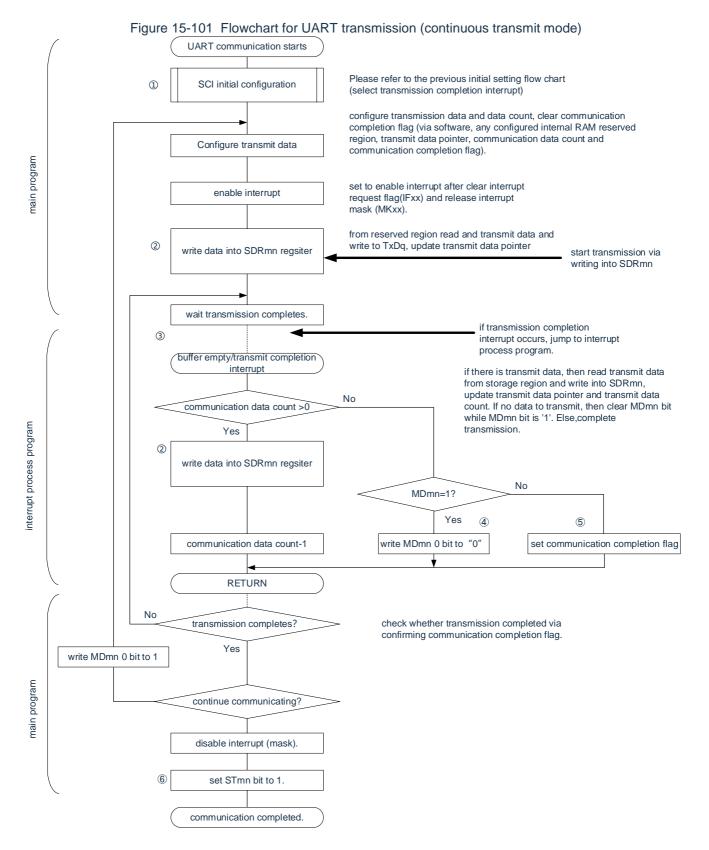

| 15.7.1 UART transmission                                                                                                       | 475  |

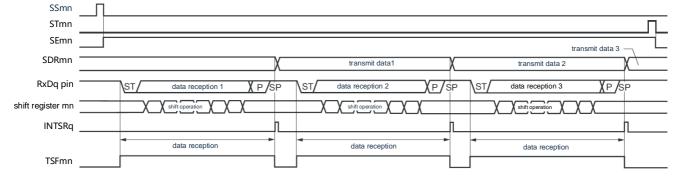

| 15.7.2 UART reception                                                                                                          |      |

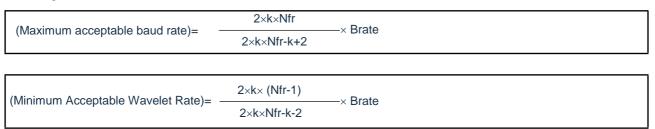

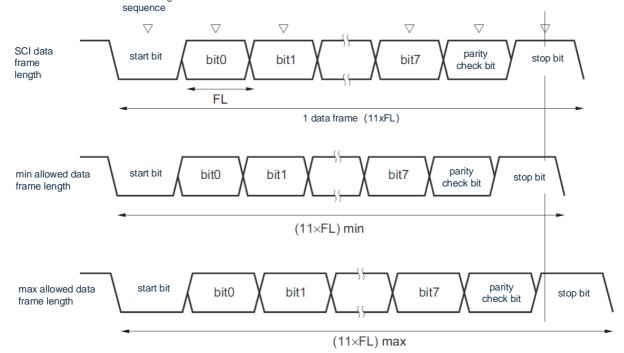

| 15.7.3 Calculation of baud rate                                                                                                | 491  |

| 15.7.4 Processing steps when an error occurs during UART (UART0~UART2) communication .                                         |      |

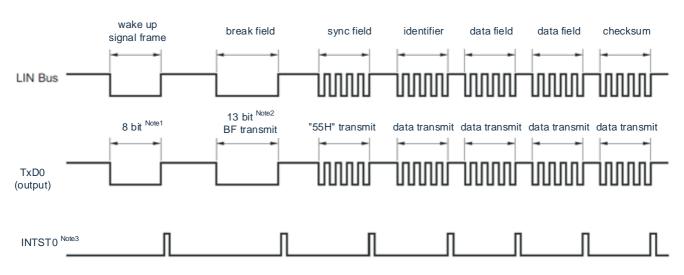

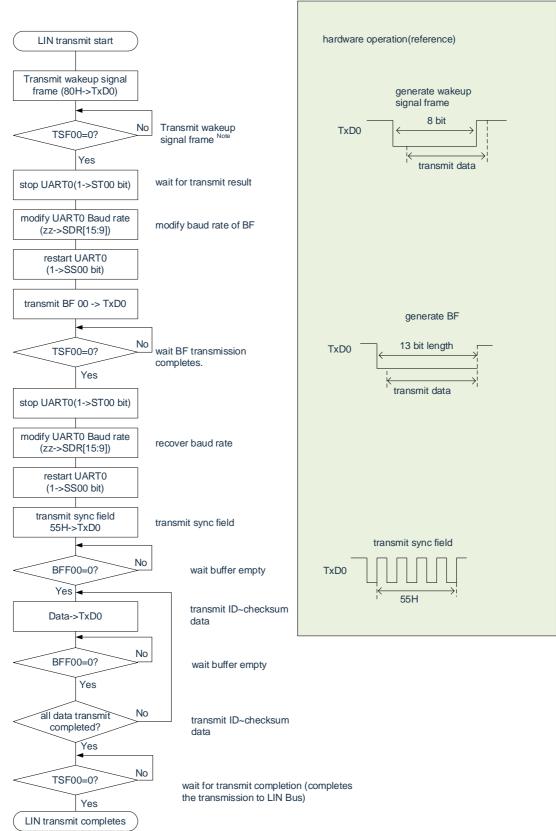

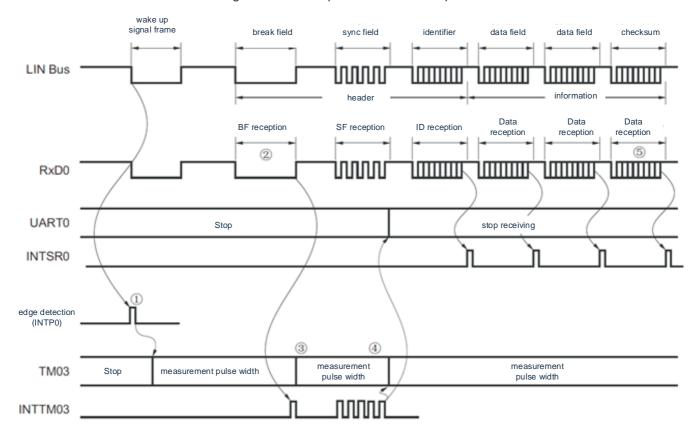

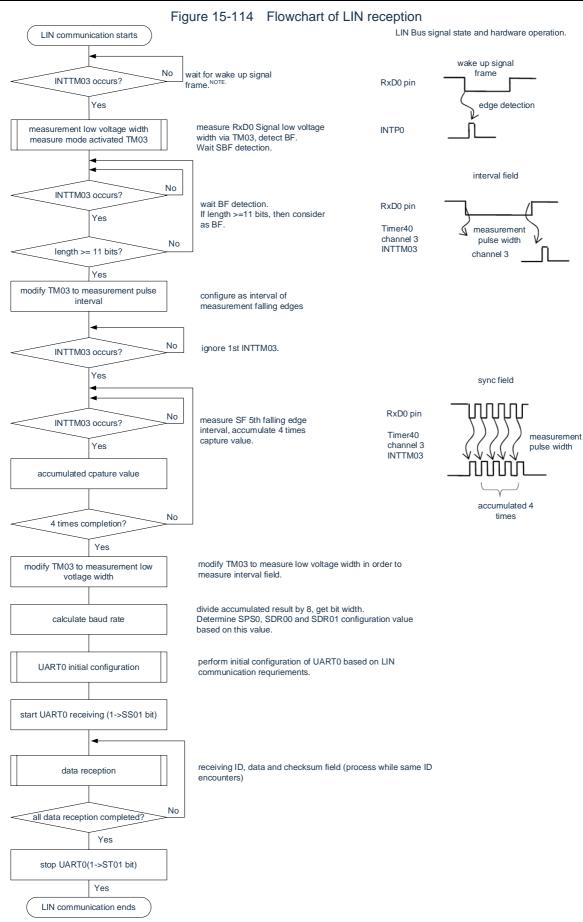

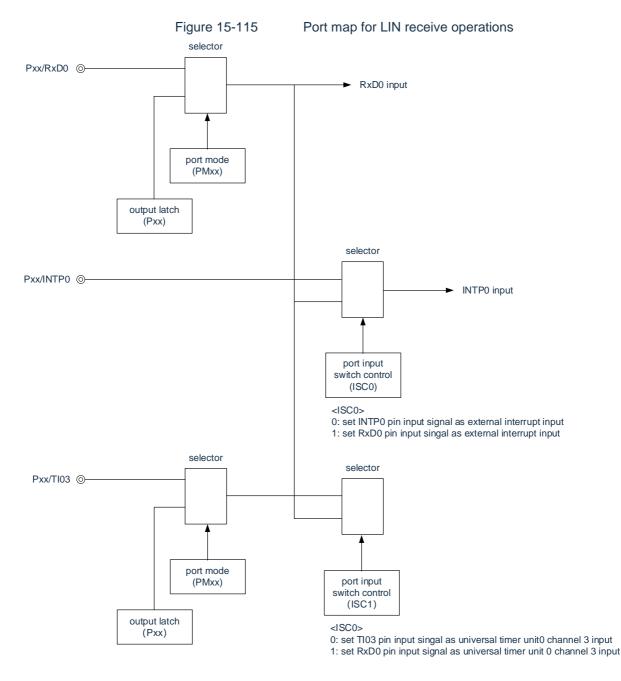

| 15.8 Operation of LIN communication                                                                                            |      |

| 15.8.1 LIN transmission                                                                                                        |      |

| 15.8.2 LIN reception                                                                                                           |      |

| 15.9 Operation of simplified I <sup>2</sup> C (IIC00, IIC01, IIC10, IIC11, IIC20,IIC21) communication                          |      |

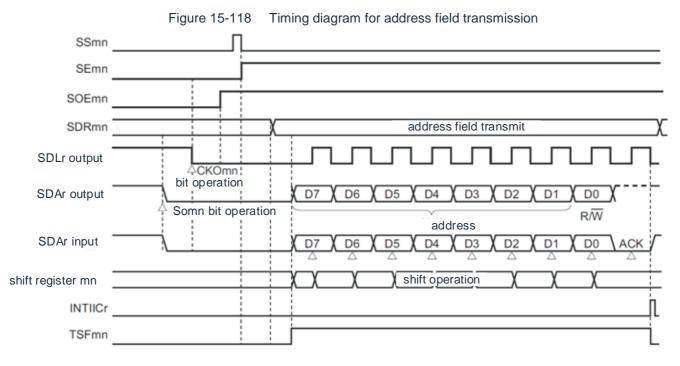

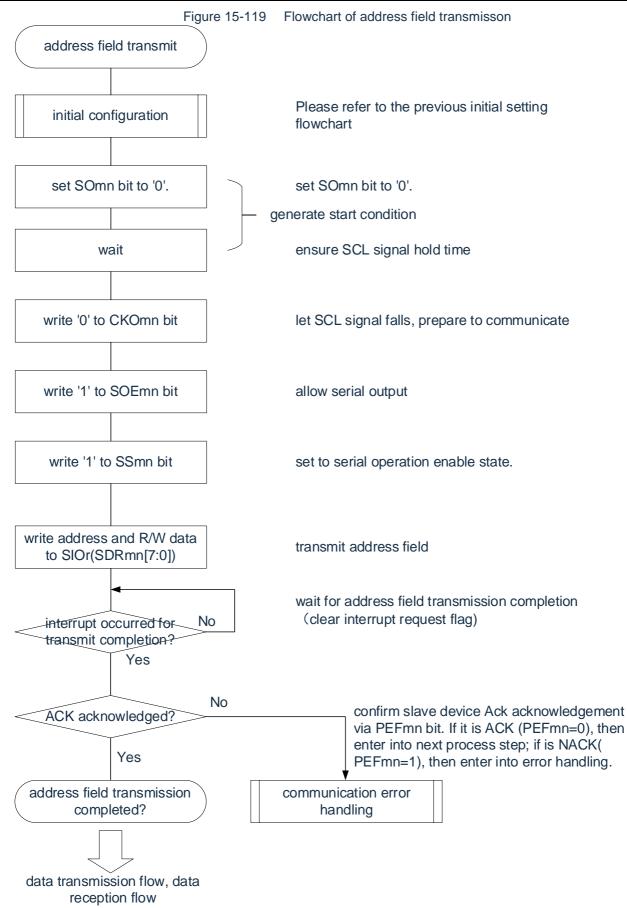

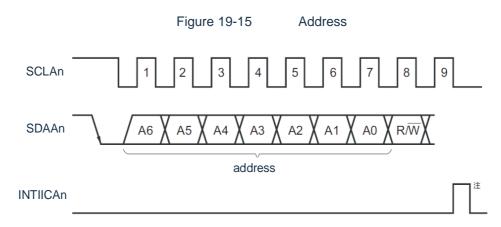

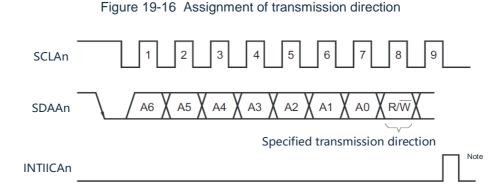

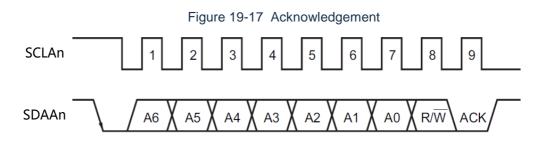

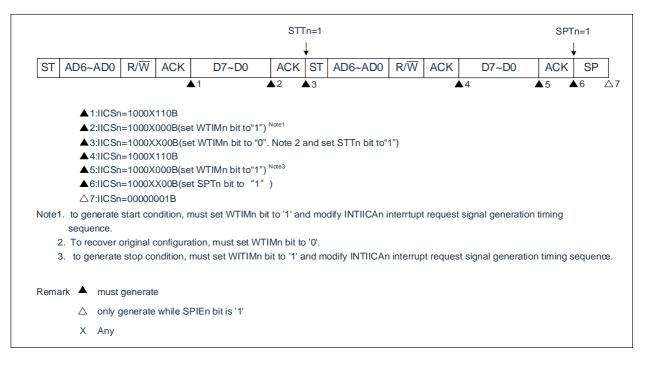

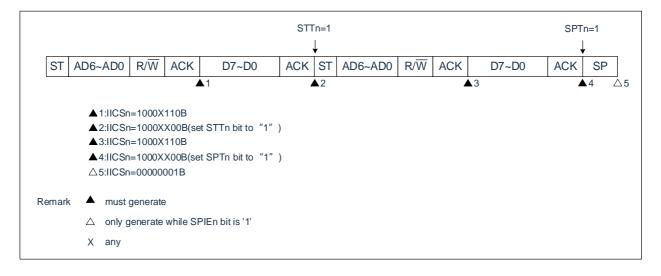

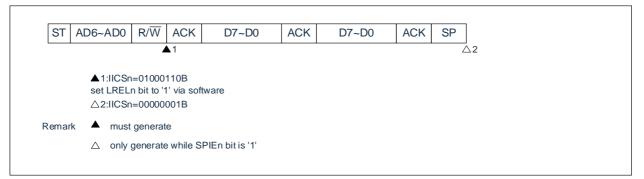

| 15.9.1 Address field transmission                                                                                              |      |

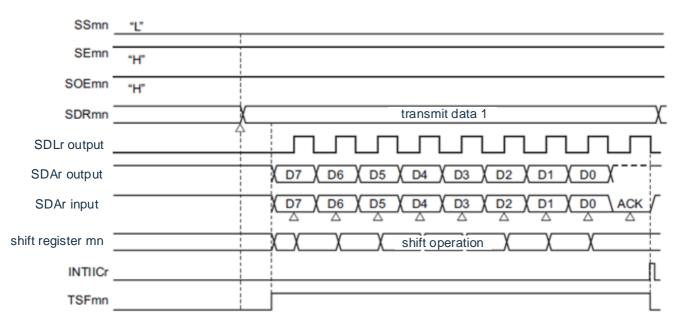

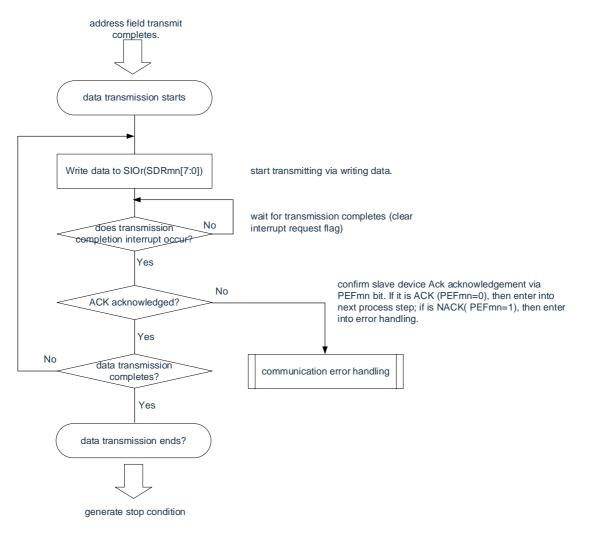

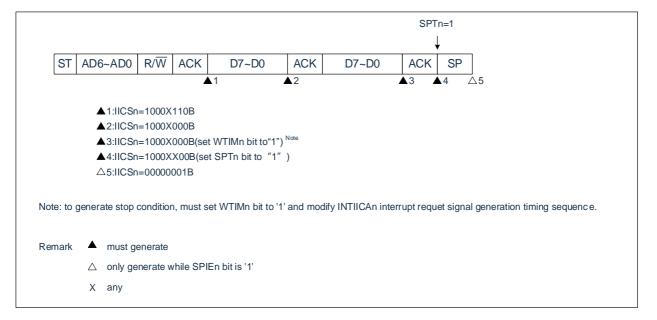

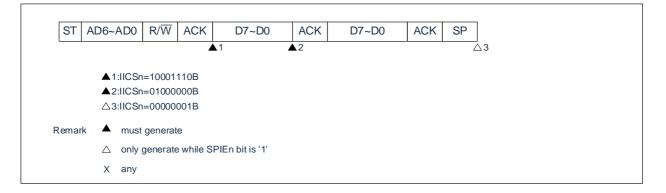

| 15.9.2 Data transmission                                                                                                       | 510  |

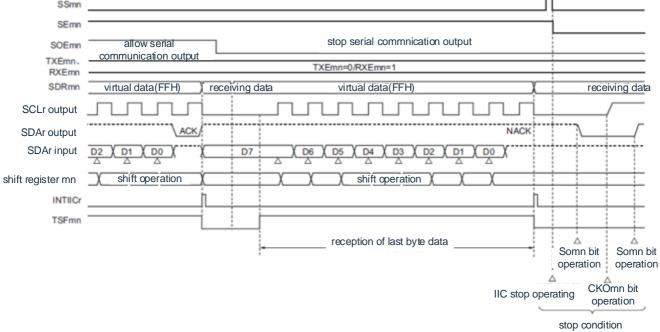

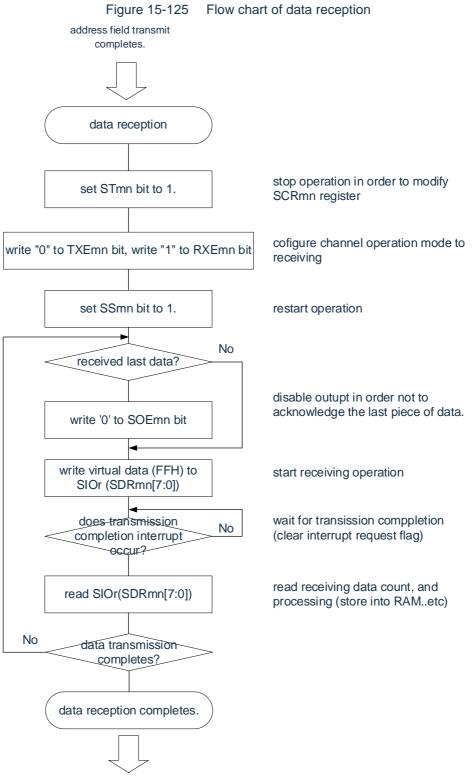

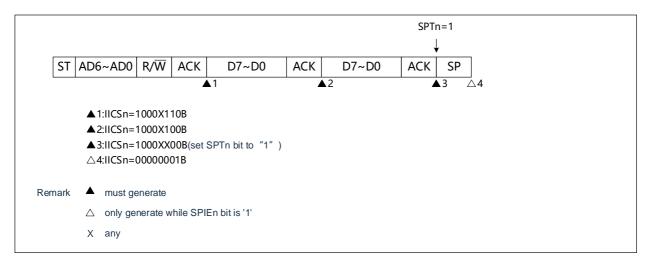

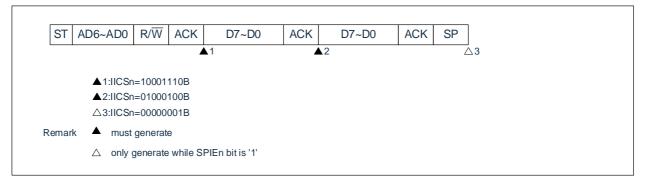

| 15.9.3 Data reception                                                                                                          | 513  |

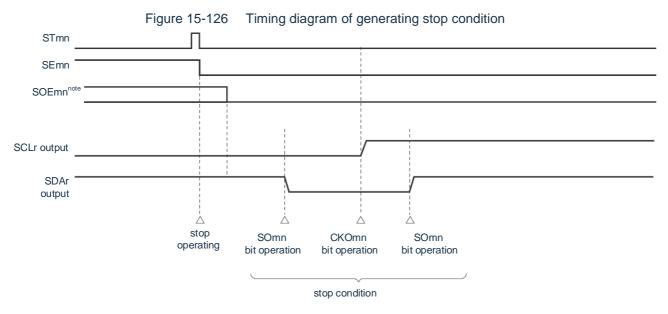

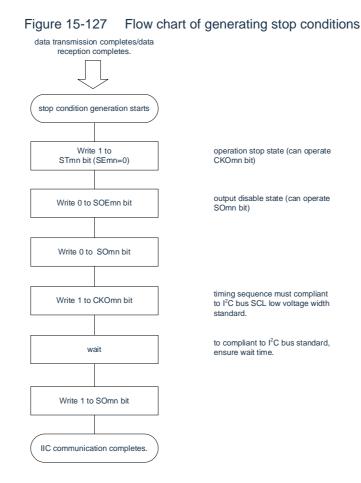

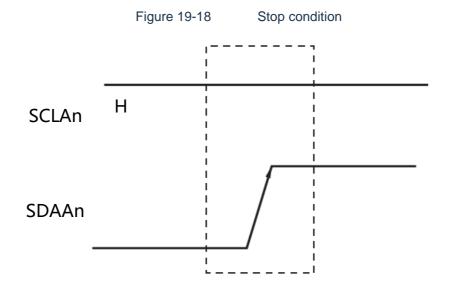

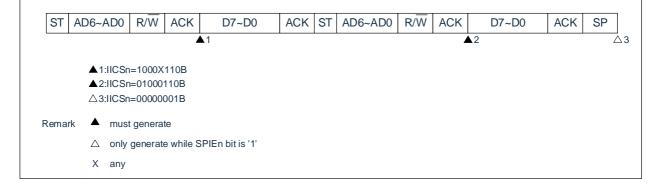

| 15.9.4 Generation of stop condition                                                                                            | 517  |

| 15.9.5 Calculation of transfer rate                                                                                            | 518  |

| 15.9.6 Procedure for handling errors during simplified I <sup>2</sup> C (IIC00, IIC01, IIC10, IIC11, IIC20, IIC2 communication |      |

| Chapter 16 Serial Interface SPI                                                                                                | 521  |

| 16.1 Function of SPI                                                                                                           | 521  |

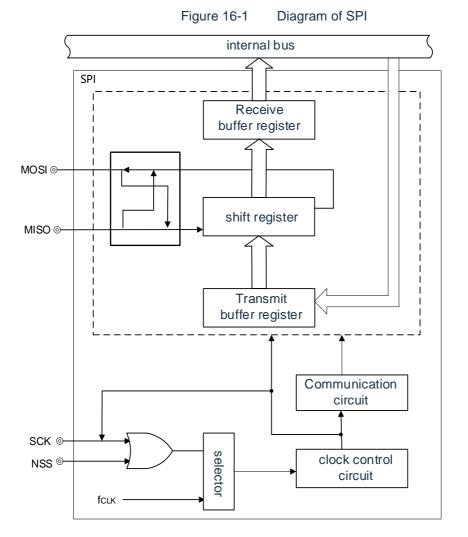

| 16.2 Structure of SPI                                                                                                          | 521  |

| 16.3 Registers for controlling SPI                                                                                             | 522  |

| 16.3.1 Peripheral enable register 1 (PER1)                                                                                     | 523  |

| 16.3.2 SPI operation mode register (SPIM)                                                                                      | 524  |

| 16.3.3 SPI clock selection register (SPICn)                                                                                    | 525  |

| 16.3.4 SPI status register (SPISn)                                                                                             |      |

| 16.3.5 Transmit buffer register (SDROn)                                                                                        | 527  |

| 16.3.6 Receive buffer register (SDRIn)                                                                                         | 527  |

| 16.3.7 Registers for controlling SPI port functions                                                                            | 528  |

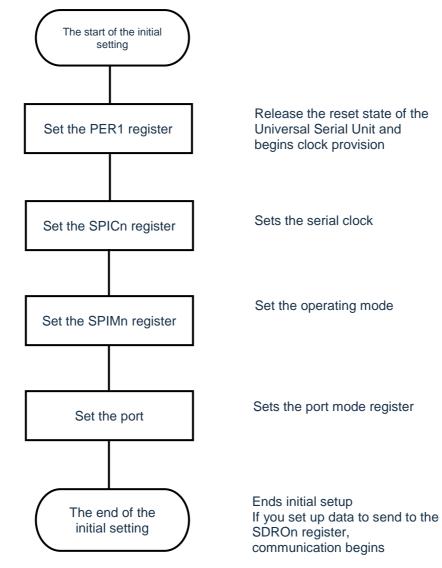

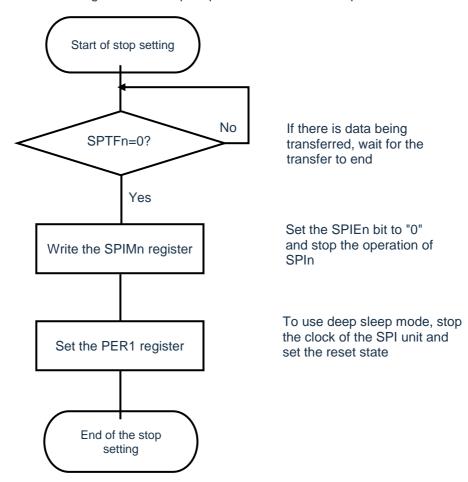

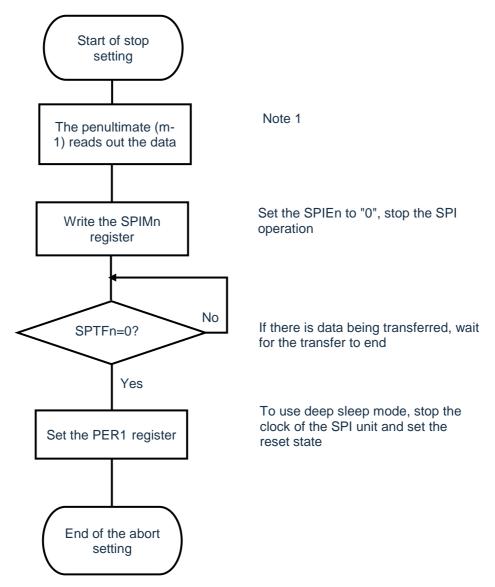

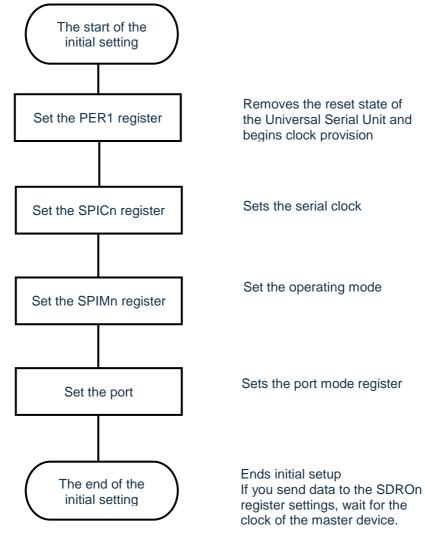

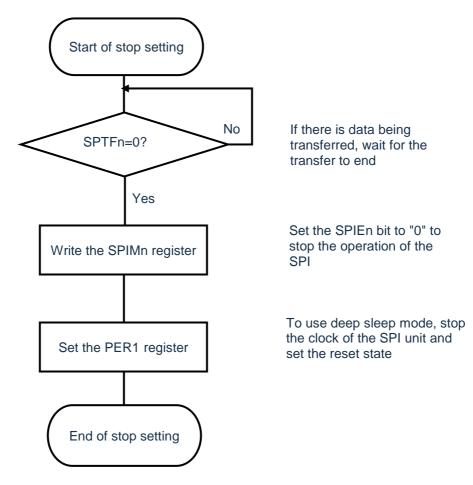

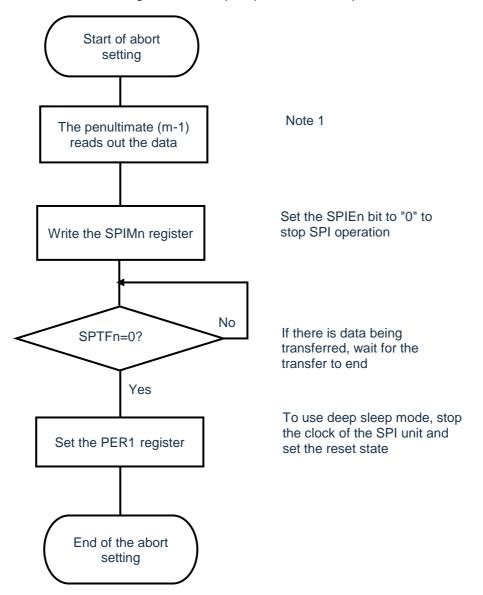

| 16.4 Operation of SPI                                                                                                          | 529  |

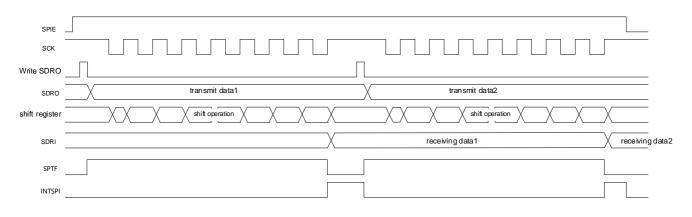

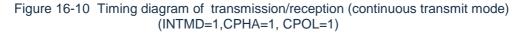

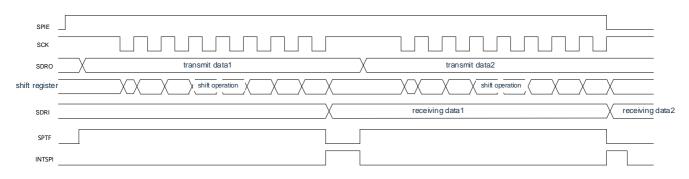

| 16.4.1 Master tramission and reception                                                                                         | 530  |

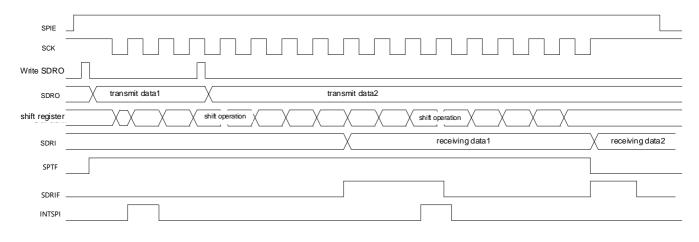

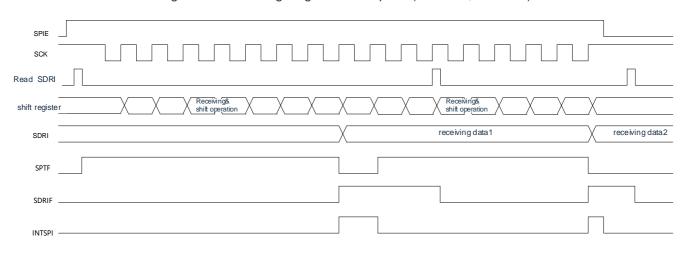

| 16.4.2 Master reception                                                                                                        | 533  |

| 16.4.3 Slave transmission and reception                                                                                        |      |

| WWW mou com cn 11 / 1025                                                                                                       | V105 |

###

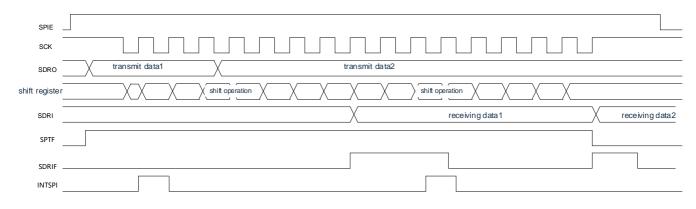

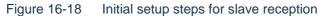

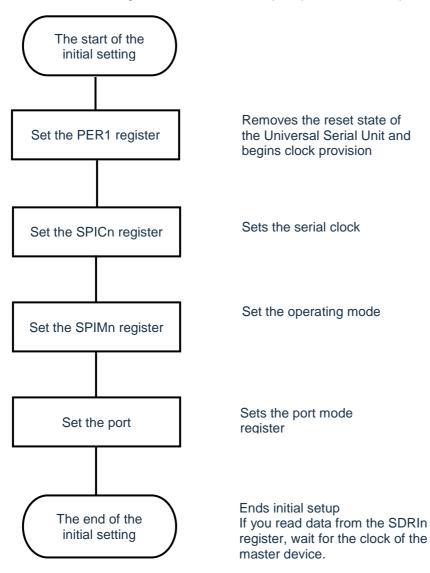

| 16.4.4 Slave reception                                   | 539  |

|----------------------------------------------------------|------|

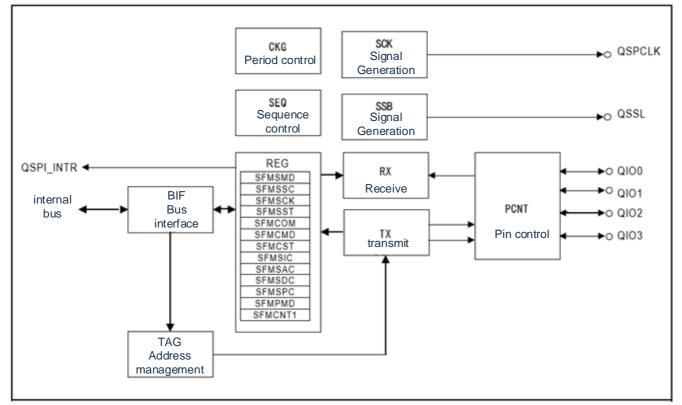

| Chapter 17 QUAD SPI                                      | 542  |

| 17.1 Overview                                            | 542  |

| 17.2 Register description                                | 544  |

| 17.2.1 Transmit mode control register (SFMSMD)           | 544  |

| 17.2.2 Chip select control register (SFMSSC)             | 546  |

| 17.2.3 Clock control register (SFMSKC)                   | 547  |

| 17.2.4 Status register (SFMSST)                          | 548  |

| 17.2.5 Communication port register (SFMCOM)              | 549  |

| 17.2.6 Communication mode control register (SFMCMD)      | 549  |

| 17.2.7 Communication status register (SFMCST)            | 549  |

| 17.2.8 Instruction code register (SFMSIC)                | 550  |

| 17.2.9 Address mode control register (SFMSAC)            | 550  |

| 17.2.10 Dummy cycle control register (SFMSDC)            | 551  |

| 17.2.11 SPI protocol control register (SFMSPC)           | 552  |

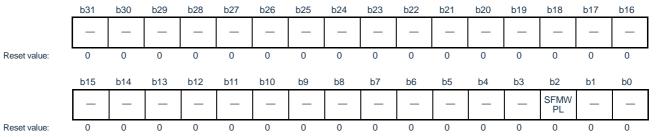

| 17.2.12 Port control register (SFMPMD)                   | 552  |

| 17.2.13 External QSPI address register (SFMCNT1)         | 553  |

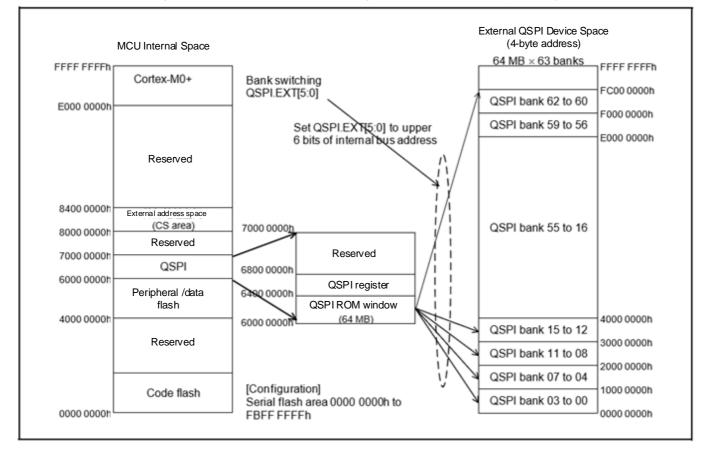

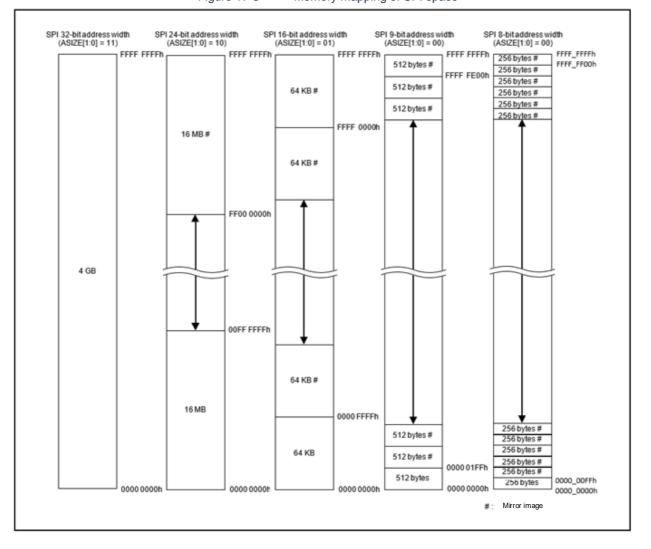

| 17.3 Memory mapping                                      | 554  |

| 17.3.1 Internal bus space                                | 554  |

| 17.3.2 SPI space and address width of SPI bus            | 555  |

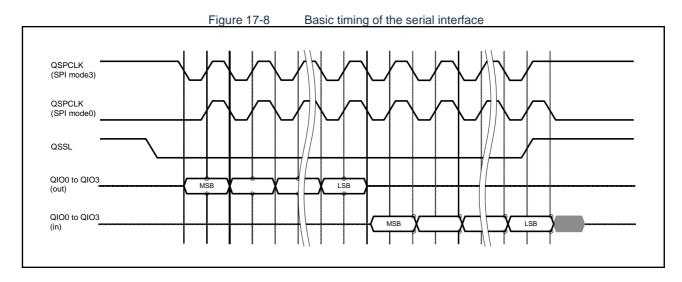

| 17.4 SPI bus                                             | 556  |

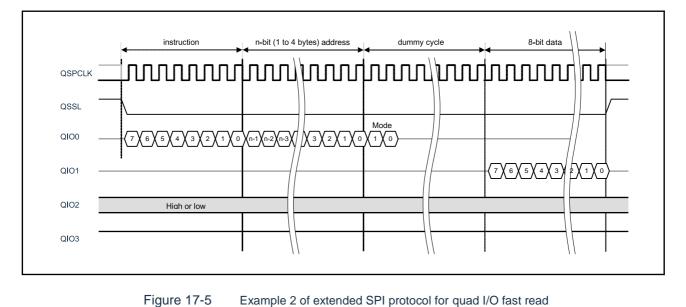

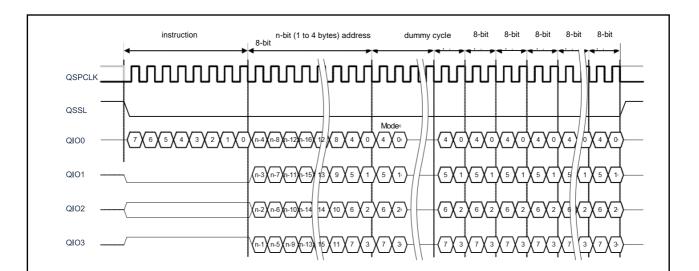

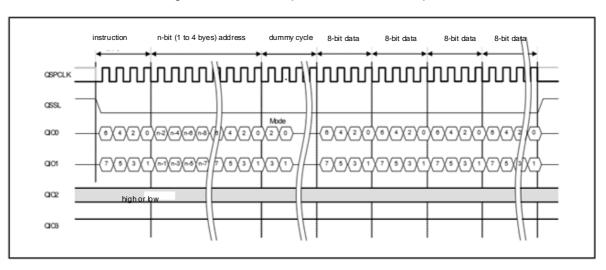

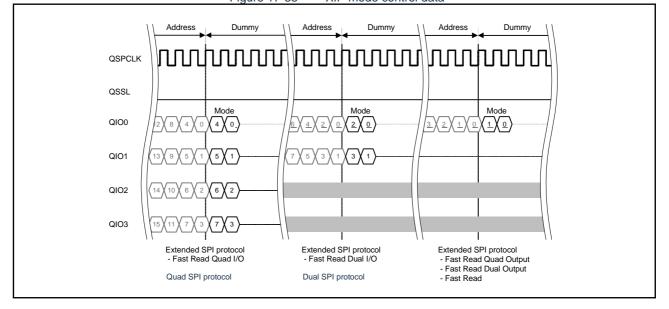

| 17.4.1 SPI protocol                                      | 556  |

| 17.4.2 SPI mode                                          | 558  |

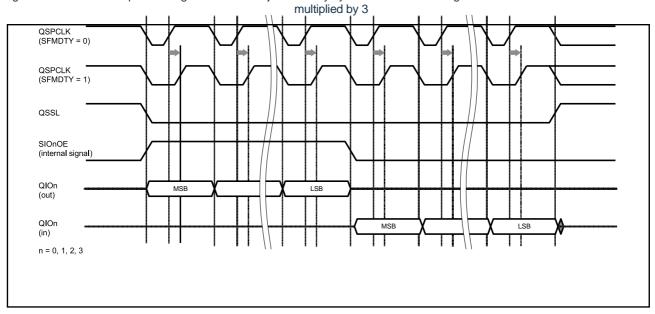

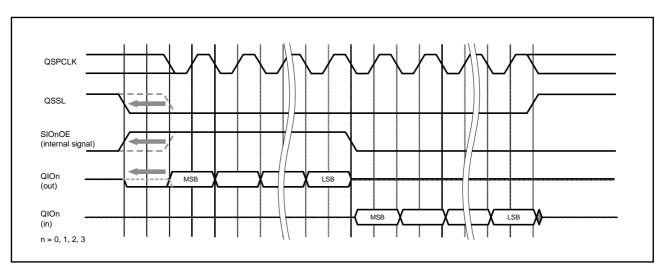

| 17.5 SPI bus timing adjustment                           | 558  |

| 17.5.1 SPI bus reference period                          | 559  |

| 17.5.2 QSPCLK signal duty cycle                          |      |

| 17.5.3 Minimum high-level width of QSSL signal           |      |

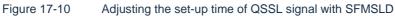

| 17.5.4 QSSL signal set-up time                           | 561  |

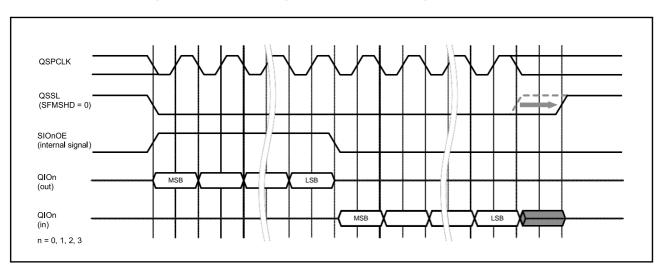

| 17.5.5 QSSL signal hold time                             | 561  |

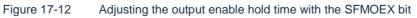

| 17.5.6 Serial data output enable hold time               | 562  |

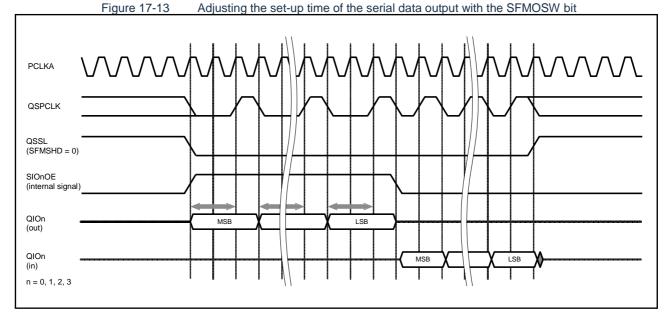

| 17.5.7 Serial data output set-up time                    | 563  |

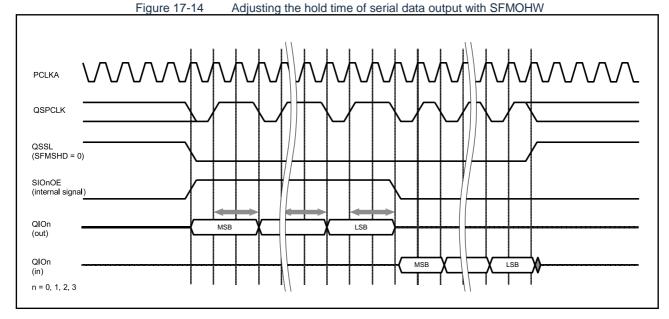

| 17.5.8 Serial data output hold time                      | 564  |

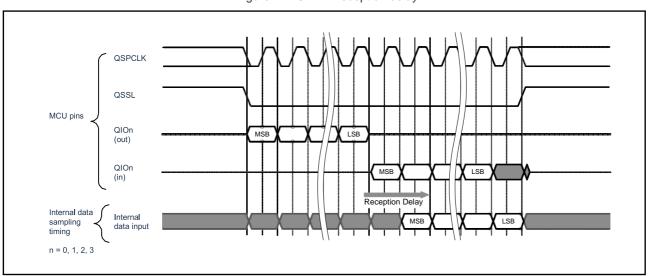

| 17.5.9 Serial data reception delay                       | 565  |

| 17.6 SPI instruction set for flash access                | 566  |

| 17.6.1 Types of automatically generated SPI instructions | 566  |

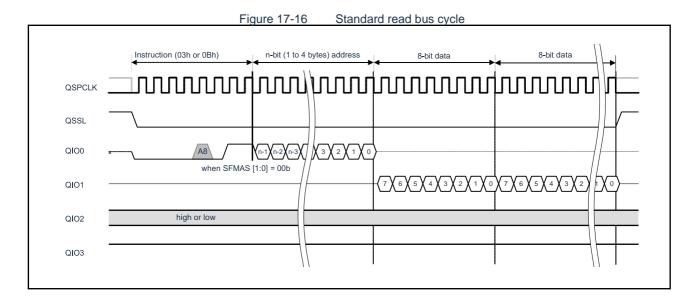

| 17.6.2 Standard read instruction                         | 568  |

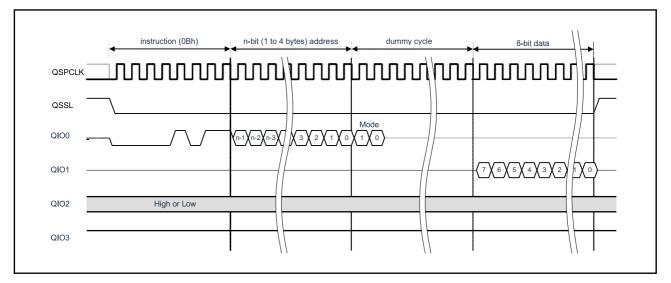

| 17.6.3 Quick read instruction                            | 569  |

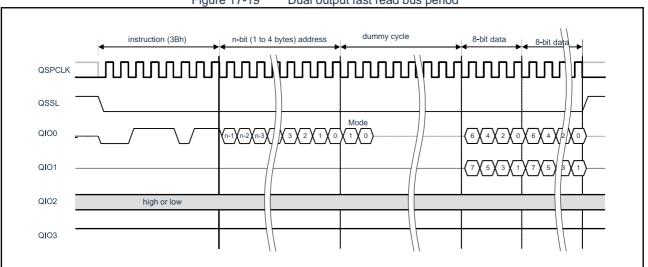

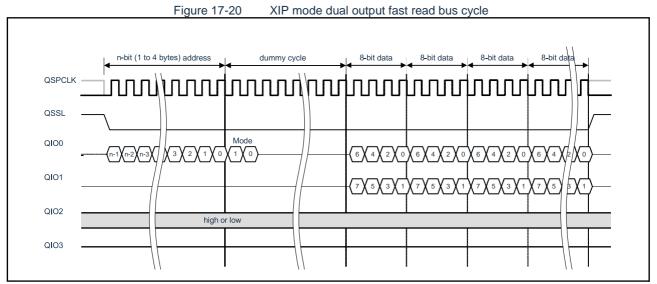

| 17.6.4 Dual output fast read instruction                 | 570  |

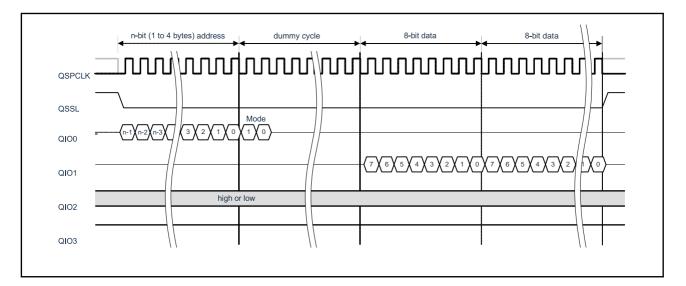

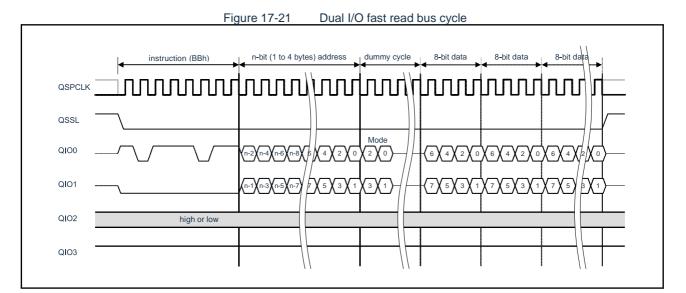

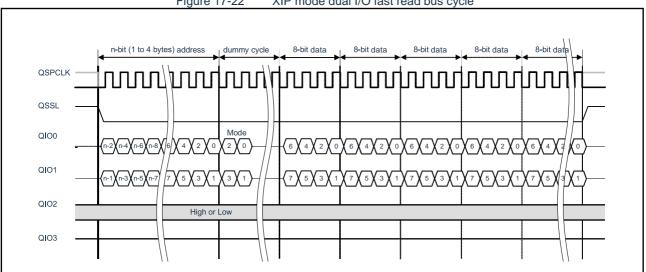

| 17.6.5 Dual I/O fast read instruction                    | 571  |

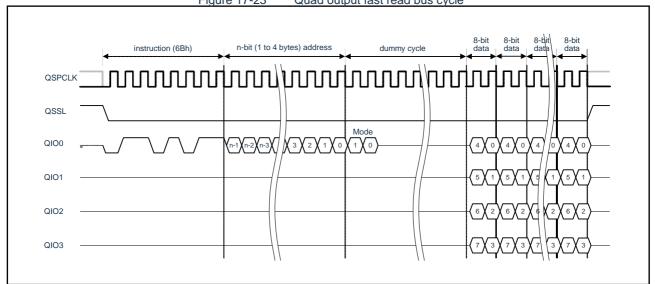

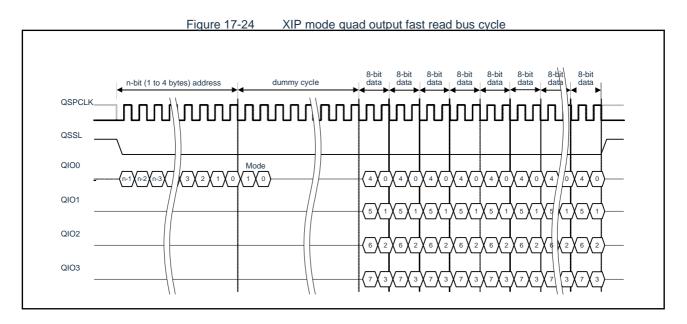

| 17.6.6 Quad output fast read instruction                 |      |

| 12 / 1025                                                | V105 |

### Cmsemicon<sup>®</sup>

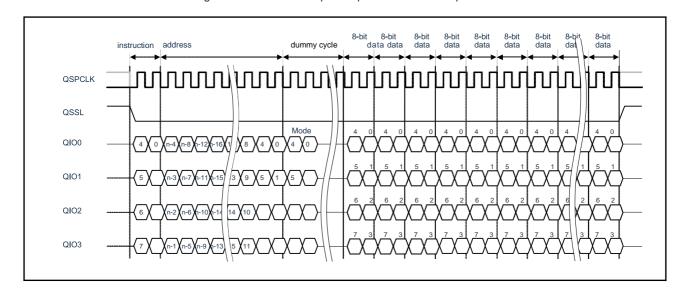

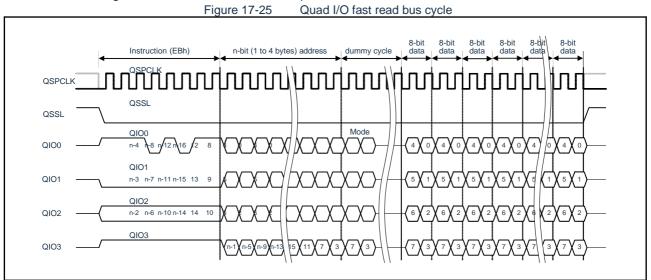

| 17.6.7 Quad I/O fast read instruction                              |        |

|--------------------------------------------------------------------|--------|

| 17.6.8 Enter 4-byte mode instruction                               | 574    |

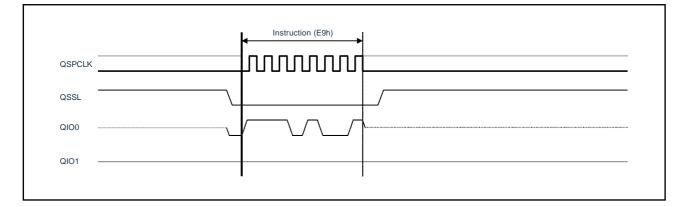

| 17.6.9 Exit 4-byte mode instruction                                |        |

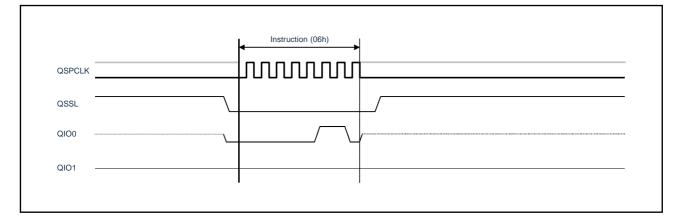

| 17.6.10 Write enable instruction                                   |        |

| 17.7 SPI bus period                                                | 576    |

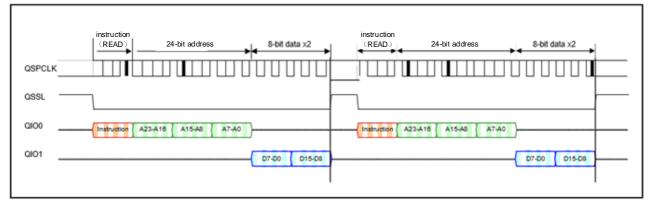

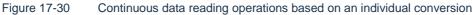

| 17.7.1 Single conversion-based flash read                          | 576    |

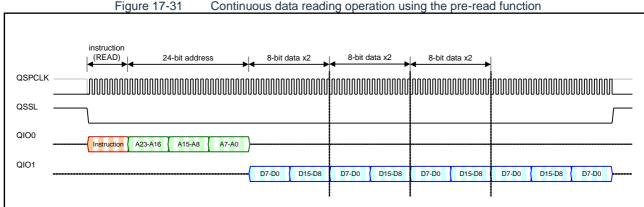

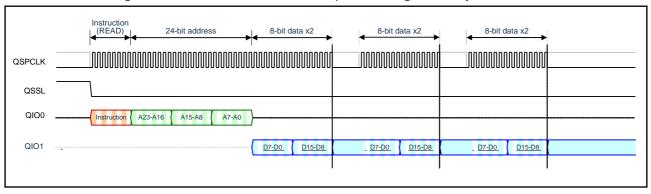

| 17.7.2 Flash memory reading with pre-read function                 |        |

| 17.7.3 Pre-read stop                                               |        |

| 17.7.4 Specify pre-reading destinations directly                   |        |

| 17.7.5 Pre-read status polling                                     |        |

| 17.7.6 Flash memory read using SPI bus cycle expansion             |        |

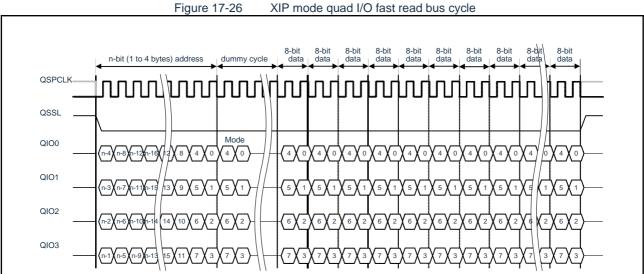

| 17.8 XIP control                                                   |        |

| 17.8.1 Setting XIP mode                                            |        |

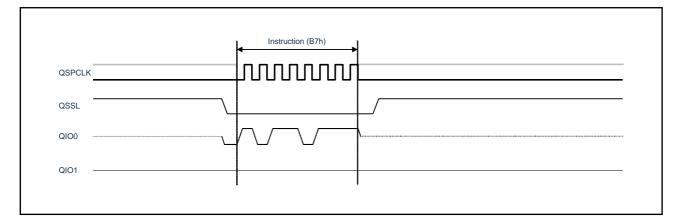

| 17.8.2 Releasing XIP mode                                          |        |

| 17.9 QIO2 and QIO3 pin status                                      |        |

| 17.10Direct communication mode                                     |        |

| 17.10.1 About direct communication                                 |        |

| 17.10.2 Direct communication mode                                  |        |

| 17.10.3 SPI bus cycles in direct communication                     |        |

| 17.11Operation                                                     |        |

| 17.11.1 Procedure for modifying multiple control register settings |        |

| 17.12Interrupt                                                     |        |

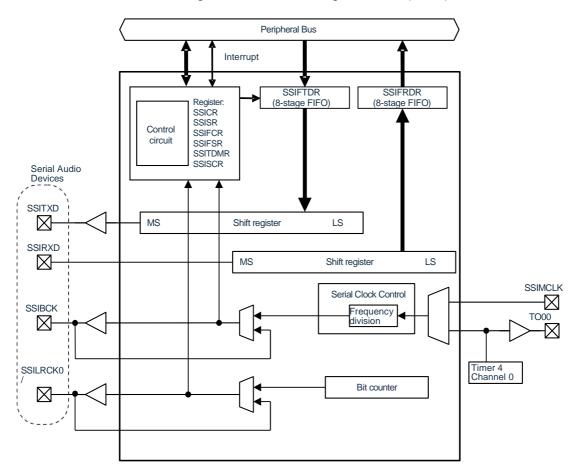

| Chapter 18 Serial Sound Interface Enhanced (SSIE)                  | 587    |

| 18.1 Overview                                                      |        |

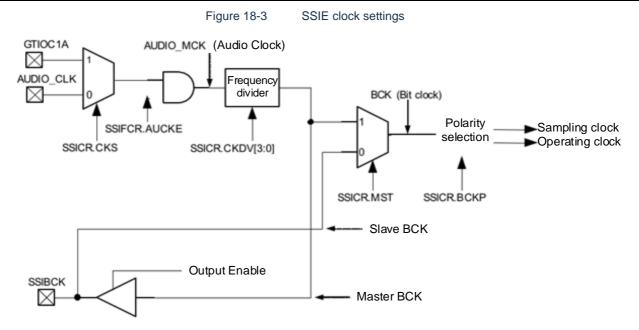

| 18.2 Specification of SSIE                                         |        |

| 18.3 Description of register                                       | 591    |

| 18.3.1 Control register (SSICR)                                    |        |

| 18.3.2 Status register (SSISR)                                     | 601    |

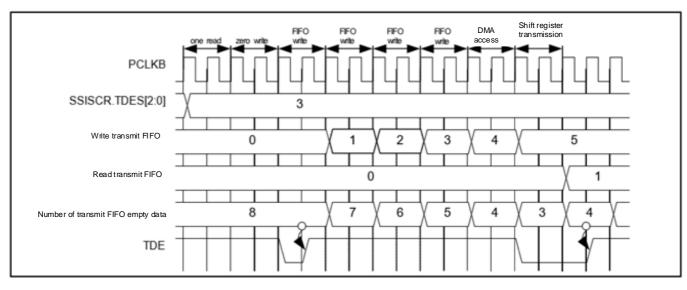

| 18.3.3 FIFO control register (SSIFCR)                              | 611    |

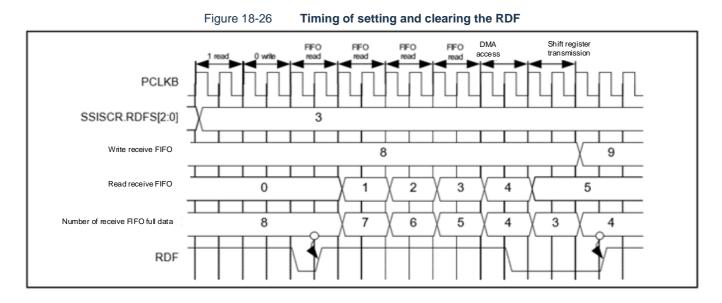

| 18.3.4 FIFO status register (SSIFSR)                               | 619    |

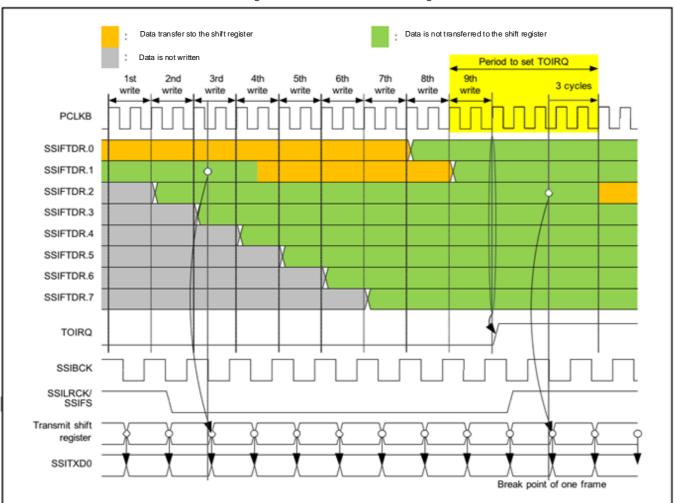

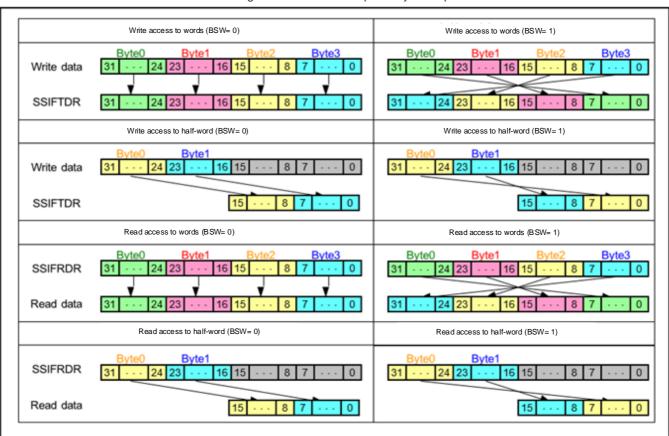

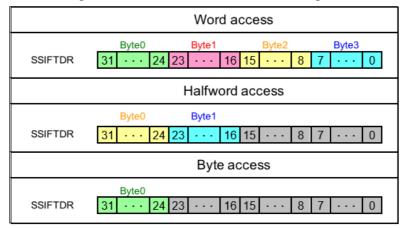

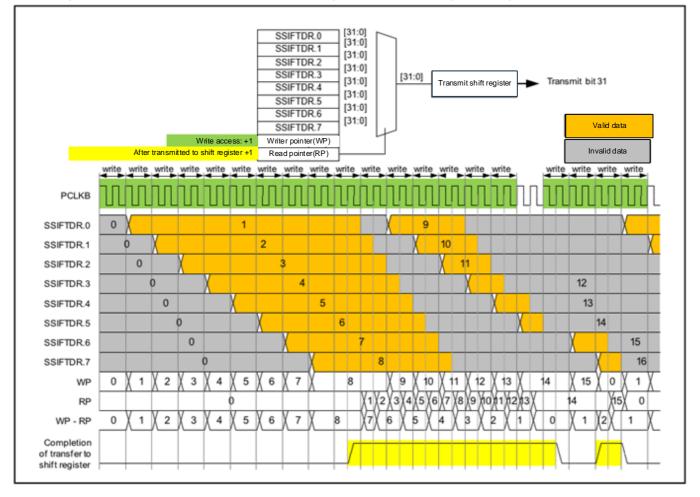

| 18.3.5 Transmit FIFO data register (SSIFTDR)                       |        |

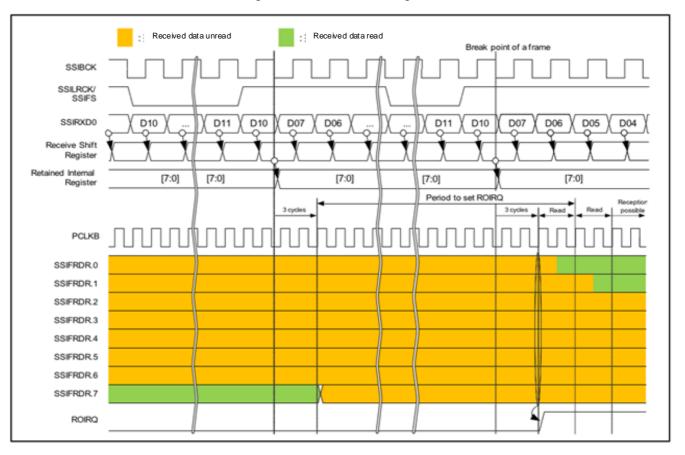

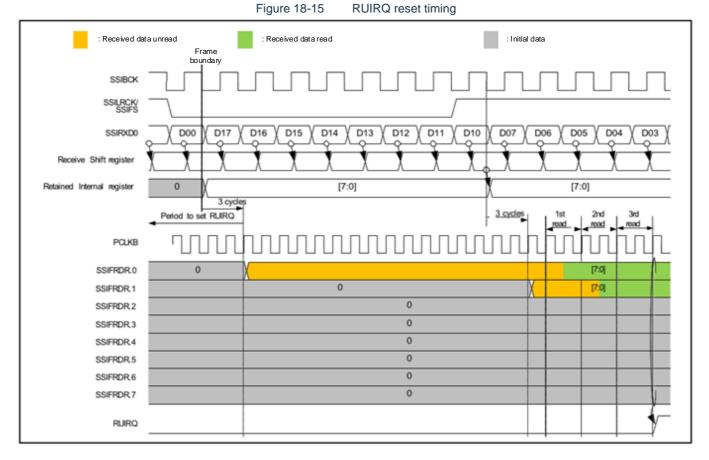

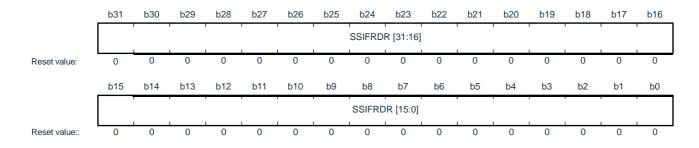

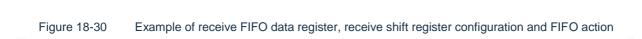

| 18.3.6 Receive FIFO data register (SSIFRDR)                        | 624    |

| 18.3.7 TDM mode register (SSITDMR)                                 |        |

| 18.3.8 Status control register (SSISCR)                            |        |

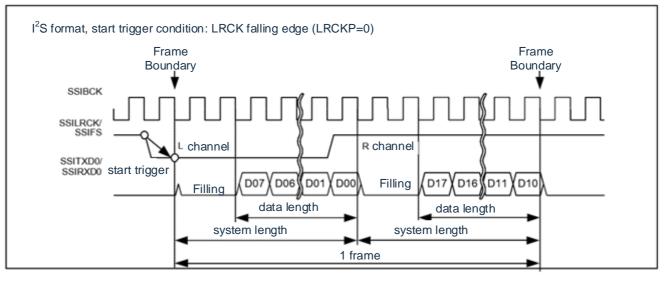

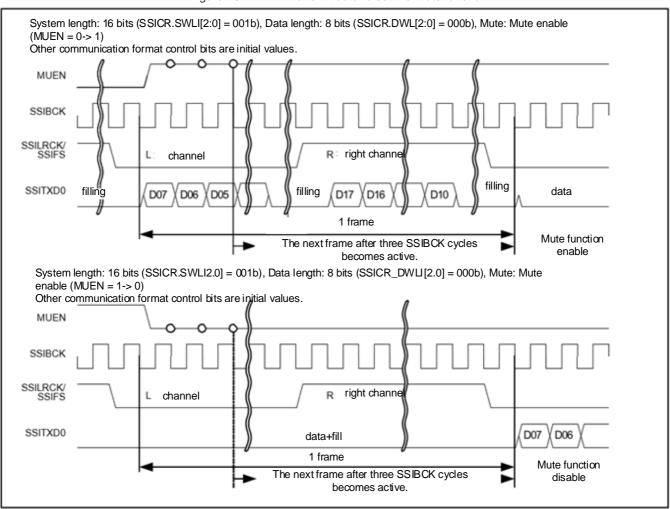

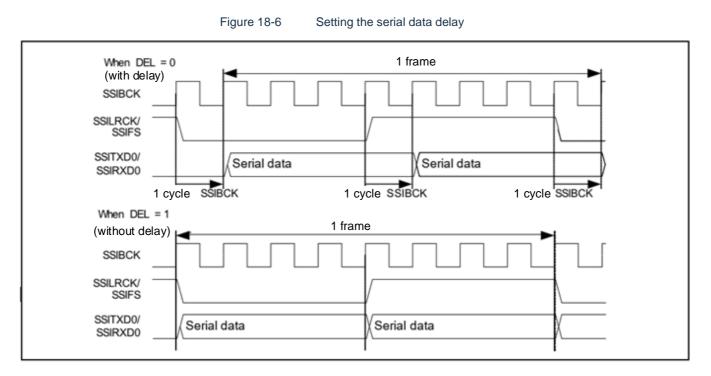

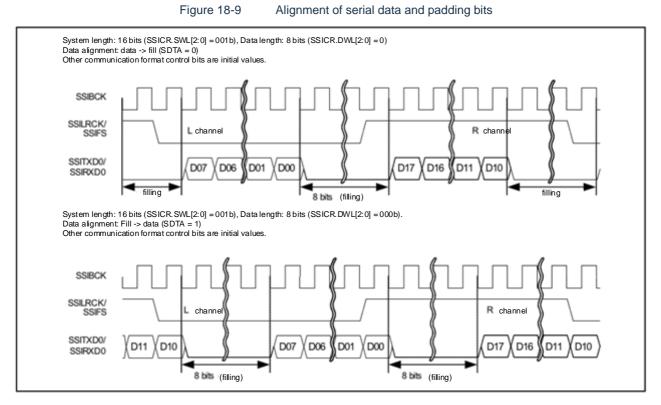

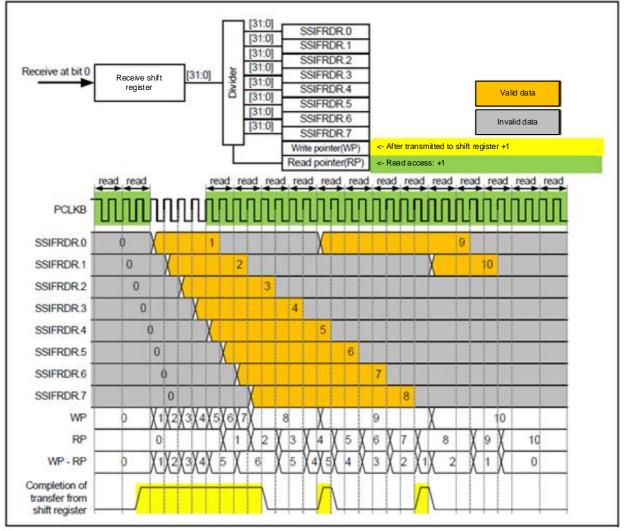

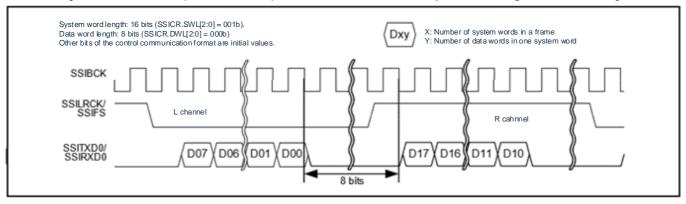

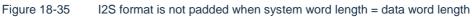

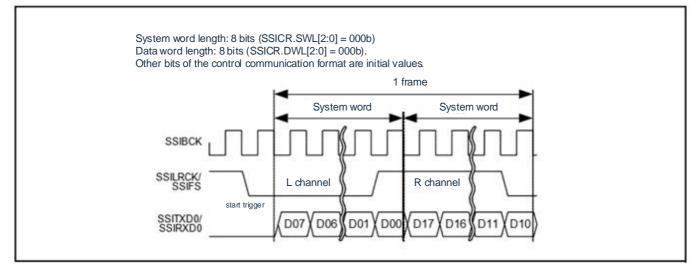

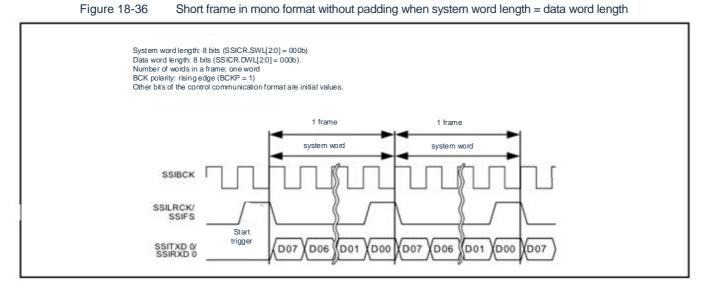

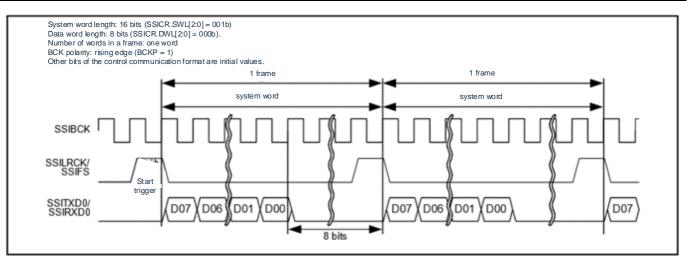

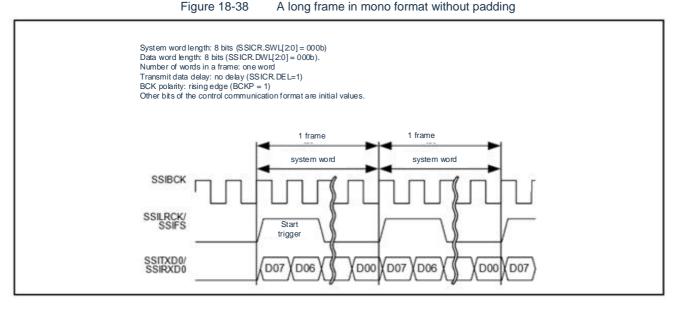

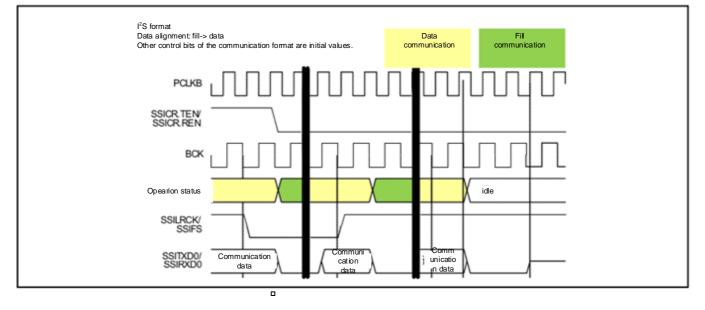

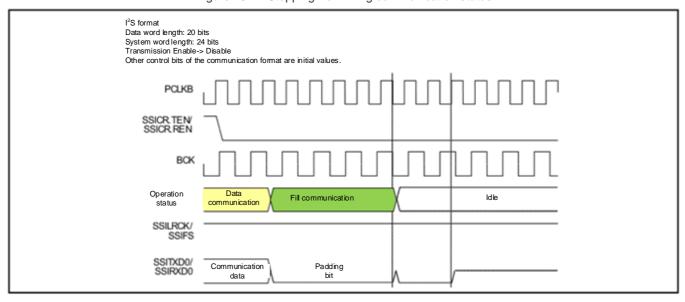

| 18.4 Communication format                                          | 630    |

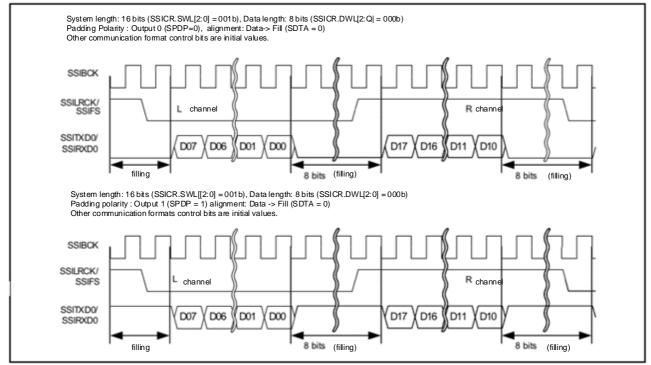

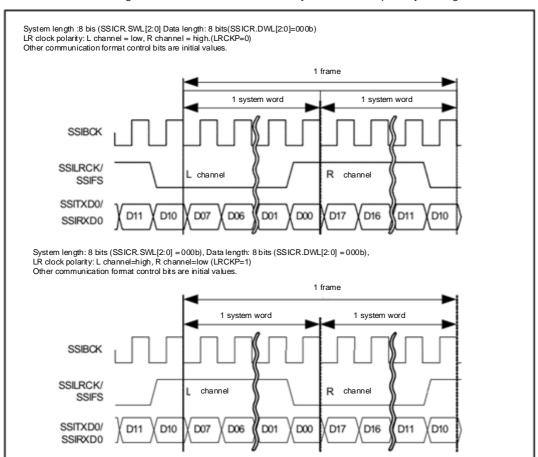

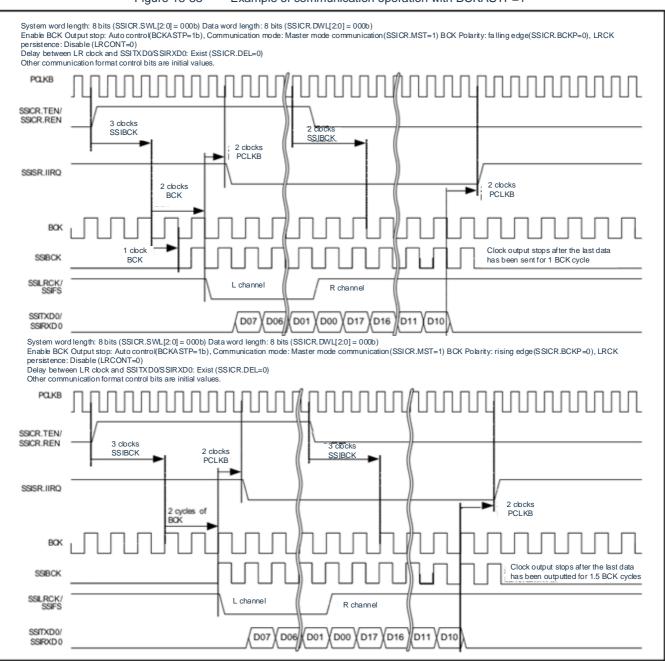

| 18.4.1 I <sup>2</sup> S format                                     | 631    |

| 18.4.2 Mono format                                                 | 631    |

| 18.5 Communication mode                                            | 634    |

| 18.5.1 Slave mode communication                                    | 635    |

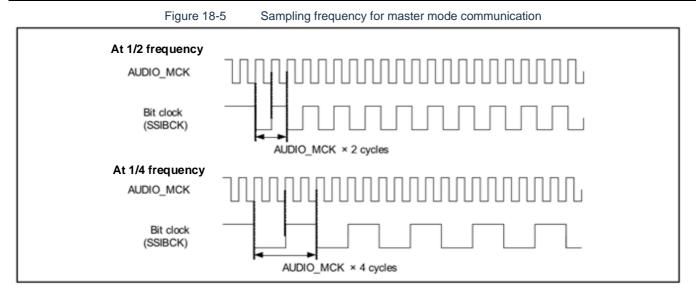

| 18.5.2 Master mode communication                                   | 635    |

| www.mcu.com.cn 13 / 1025                                           | V1.0.5 |

| 18.5.4       Reception       635         18.5.5       Transmission and reception       635         18.6       Operation       636         18.6.1       Idle status       636         18.6.2       Communication operation       642         18.7       Communication operation       643         18.7.2       Transmission       644         18.7.3       Reception       644         18.7.4       Transmission and reception       645         18.7.5       Stopping communication       646         18.7.6       Error handling       648         18.7.7       Restoring communication       651         18.8       Interrupt       651         18.8.1       SSIEO_SSITXI interrupt       651         18.8.2       SSIEO_SSITXI interrupt (full duplex communication)       652         18.8.3       SSIEO_SSITXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.10.2       Cautions for naster mode communication       655         18.10.2       Cautions for naster mode communication       655         18.10.2       Cautions for raster mode communication       655         18.10.2       Cautions for ra                                                                                                                           | 18.5.3  | Transmission                                                                                     | 635 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------|-----|

| 18.6 Operation       636         18.6.1 Idle status       636         18.6.2 Communication status       638         18.7 Communication operation       642         18.7.1 Starting communication       643         18.7.2 Transmission       644         18.7.3 Reception       645         18.7.4 Transmission       644         18.7.5 Stopping communication       646         18.7.6 Error handling       646         18.7.7 Restoring communication       651         18.8.1 SSIEO_SSIF Interrupt       651         18.8.2 SSIEO_SSITXI interrupt (full duplex communication)       652         18.8.3 SSIEO_SSITXI interrupt (full duplex communication)       652         18.9 Soft reset       653         18.1 Cautions       655         18.10.2 Cautions for master mode communication       655         18.10.2 Cautions for omster mode communication       655         18.10.2 Cautions for communication process       655         18.10.3 Cautions for communication process       655         18.10.4 Write access restrictions       657         19.1 Function of serial interface IICA       659         19.1.1 Idle mode       659         19.1.2 If C bus mode (multi-master capable)       659                                                                             | 18.5.4  | Reception                                                                                        | 635 |

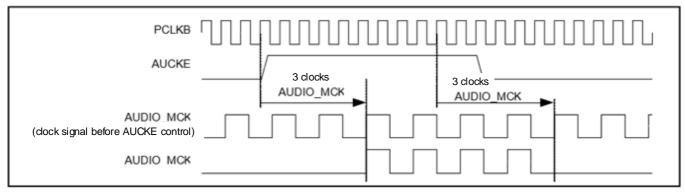

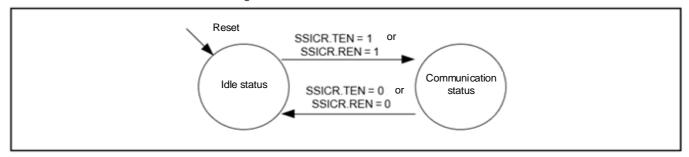

| 18.6.1       Idle status       636         18.6.2       Communication status       638         18.7       Communication operation       642         18.7.1       Stating communication       643         18.7.2       Transmission       644         18.7.3       Reception       645         18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       650         18.8       Interrupt       651         18.8.1       SSIEO_SSIF interrupt.       651         18.8.1       SSIEO_SSIRXI interrupt (full duplex communication)       652         18.8.3       SSIEO_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.9 If reset process       653         18.10 Cautions       655         18.10.2 Cautions for slave mode communication       655         18.10.3 Cautions for communication process       656         18.10.4 Write access restrictions       657         19.1 Function of serial interface IICA       659         19.1.1       Ide mode       <                                                                                                                      | 18.5.5  | Transmission and reception                                                                       | 635 |

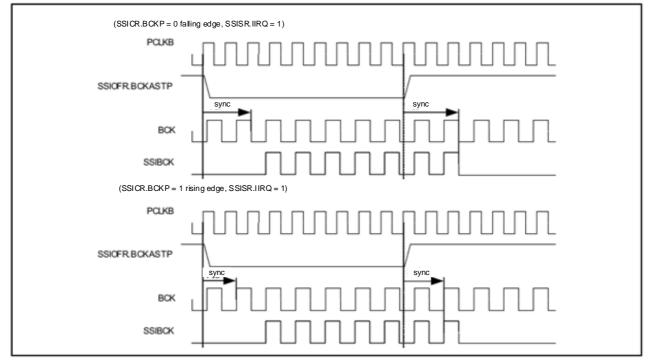

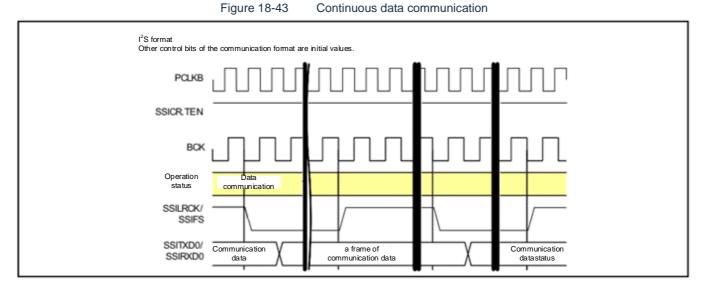

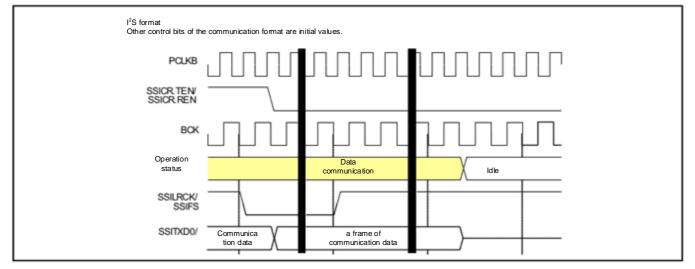

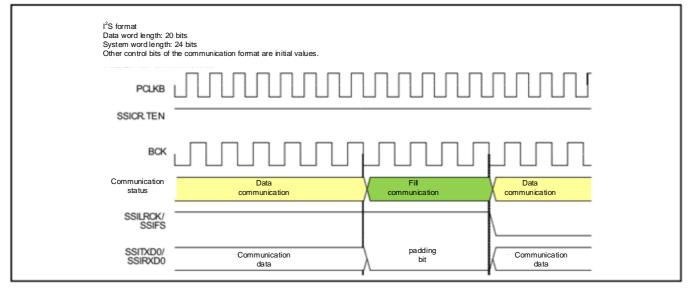

| 18.6.2       Communication status       638         18.7       Communication operation       642         18.7.1       Starting communication       643         18.7.2       Transmission       644         18.7.3       Reception       645         18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       650         18.8       Interrupt       651         18.8.1       SIEO_SSIF Interrupt.       651         18.8.2       SIEO_SSIFXI Interrupt (full duplex communication)       652         18.8.3       Soft reset       653         18.9       Soft reset process       653         18.10       Salico_SSIRXI Interrupt (full duplex communication)       652         18.8       Soft reset process       653         18.9       Soft reset process       653         18.10.1       Cautions for alave mode communication       655         18.10.2       Cautions for communication process       656         18.10.3       Cautions for communication process       656         18.10.4       Write acces                                                                                                                           | 18.6 O  | peration                                                                                         | 636 |

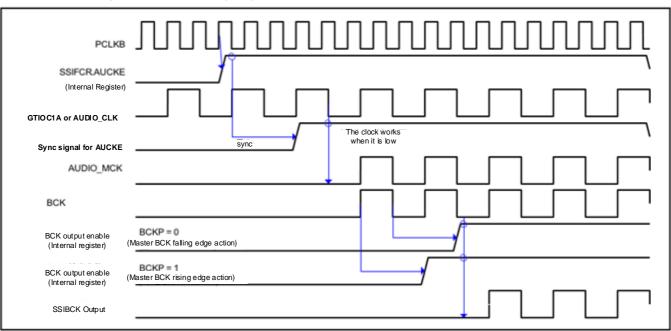

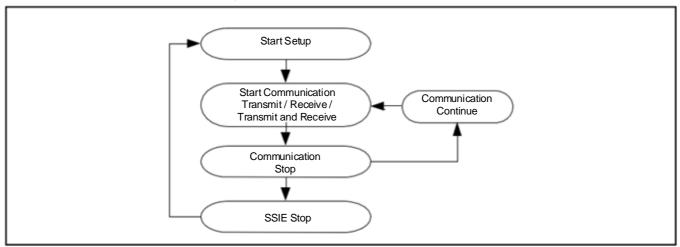

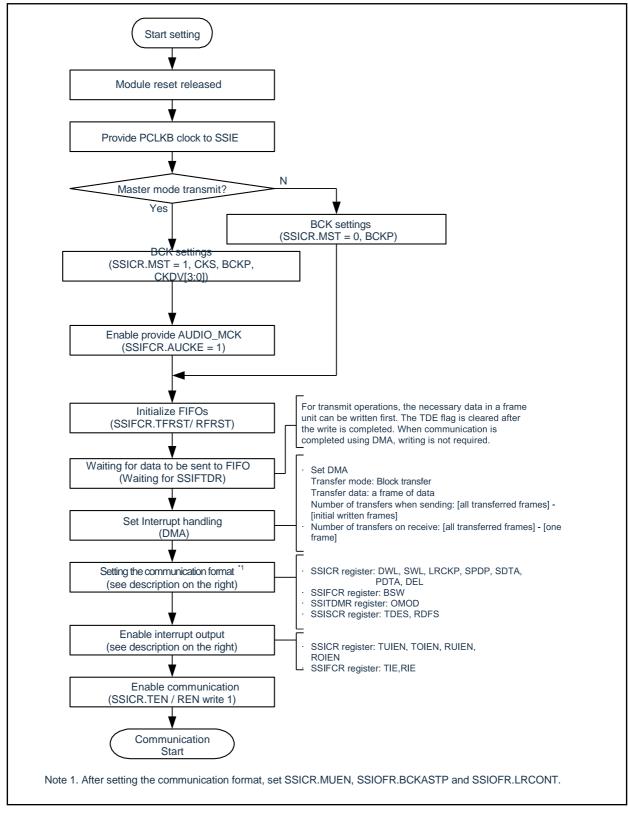

| 18.7 Communication operation       642         18.7.1 Starting communication       643         18.7.2 Transmission       644         18.7.3 Reception       644         18.7.4 Transmission and reception       646         18.7.5 Stopping communication       647         18.7.7 Restoring communication       648         18.7.7 Restoring communication       650         18.8 Interrupt       651         18.8.1 SSIE0_SSIF Interrupt       651         18.8.2 SSIE0_SSIFXI interrupt (full duplex communication)       652         18.8.3 SSIE0_SSIRXI interrupt (full duplex communication)       652         18.8.3 SSIE0_SSIRXI interrupt (full duplex communication)       655         18.9 Soft reset       653         18.01 Cautions for slave mode communication.       655         18.10.2 Cautions for communication       655         18.10.3 Cautions for communication       655         18.10.4 Write access restrictions       657         Chapter 19 Serial Interface IICA       659         19.1.1 Idle mode       659         19.1.2 IPC bus mode (multi-master capable)       659         19.1.3 Wake-up mode       659         19.2.2 Structure of serial interface IICA       659         19.2.3 SO latch       664 <td>18.6.1</td> <td>Idle status</td> <td>636</td> | 18.6.1  | Idle status                                                                                      | 636 |

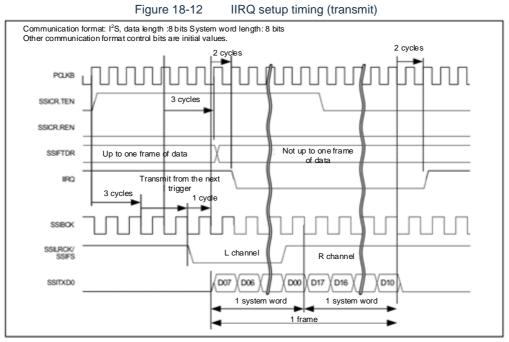

| 18.7.1       Starting communication       643         18.7.2       Transmission       644         18.7.3       Reception       645         18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       651         18.8       Interrupt       651         18.8.1       SSIE0_SSIF Interrupt       651         18.8.2       SSIE0_SSITXI interrupt (full duplex communication)       652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.9       Soft reset       653         18.10Cautions for slave mode communication       655         18.10.2       Cautions for slave mode communication       655         18.10.2       Cautions for communication process       656         18.10.4       Write access restrictions       657         18.10.4       Write access restrictions       657         18.10.4       Write access restrictions       656         18.10.4       Write access restrictions       659         19.1.1       Ide m                                                                                                                  | 18.6.2  | Communication status                                                                             | 638 |

| 18.7.2       Transmission       644         18.7.3       Reception       645         18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       650         18.8       Interrupt       651         18.8.1       SSIEO_SSIF interrupt       651         18.8.2       SSIEO_SSIRXI interrupt (full duplex communication)       652         18.8.3       SSIEO_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.10Cautions       655       653         18.10Cautions       655       651         18.10Cautions for slave mode communication       655         18.10.2 Cautions for master mode communication       655         18.10.2 Cautions for communication process       656         18.10.4 Write access restrictions       657         Chapter 19 Serial Interface IICA       659         19.1.1       Icle bus mode       659         19.1.2       I/2 bus mode (multi-master capable)       659         19.2.2       Slave address register n (IICAn)       663                                                                                                                   | 18.7 C  | ommunication operation                                                                           | 642 |

| 18.7.3       Reception       645         18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       650         18.8       Interrupt       651         18.8.1       SSIE0_SSIF interrupt       651         18.8.1       SSIE0_SSITXI interrupt (full duplex communication)       652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.9.1       Soft reset       653         18.9.1       Soft reset       653         18.9.2       Cautions for slave mode communication       655         18.10.2       Cautions for slave mode communication       655         18.10.3       Cautions for communication process       656         18.10.4       Write access restrictions       657         18.14       Write access restrictions       657         18.14       Write access restrictions       656         18.10.4       Write access restrictions       657         19.1       Idef mode       659 <t< td=""><td>18.7.1</td><td>Starting communication</td><td>643</td></t<>                                    | 18.7.1  | Starting communication                                                                           | 643 |

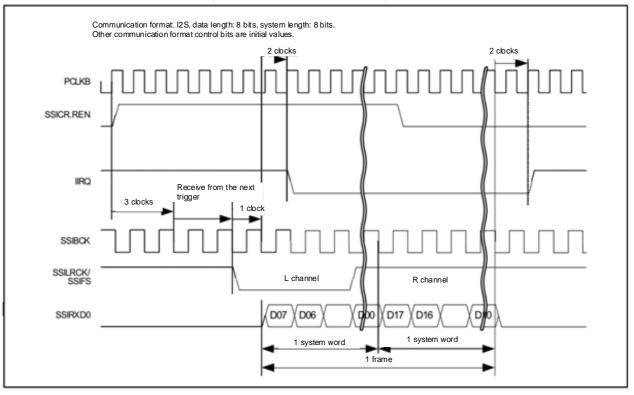

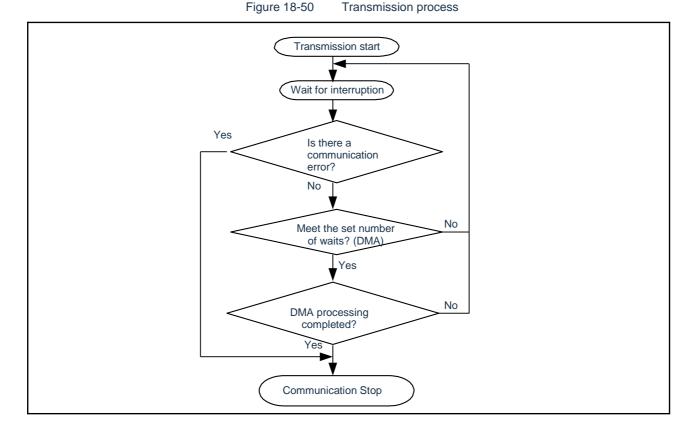

| 18.7.4       Transmission and reception       646         18.7.5       Stopping communication       647         18.7.6       Error handling       648         18.7.7       Restoring communication       650         18.8       Interrupt       651         18.8.1       SSIE0_SSIF interrupt       651         18.8.2       SSIE0_SSIXI interrupt (full duplex communication)       652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.0.1       Cautions for slave mode communication       655         18.10.2       Cautions for slave mode communication       655         18.10.2       Cautions for master mode communication       655         18.10.2       Cautions for communication process       655         18.10.3       Cautions for communication process       655         18.10.4       Write access restrictions       657         Chapter 19       Serial Interface IICA       659         19.1.1       Ide mode       659         19.1.2       IPC bus mode (multi-master capable)       659         19.1.2       IPC bus mode (multi-master capable)       659         19.1.3       Wake-up mode                                                                                    | 18.7.2  | Transmission                                                                                     | 644 |

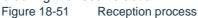

| 18.7.5       Stopping communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18.7.3  | Reception                                                                                        | 645 |

| 18.7.6       Error handling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18.7.4  | Transmission and reception                                                                       | 646 |

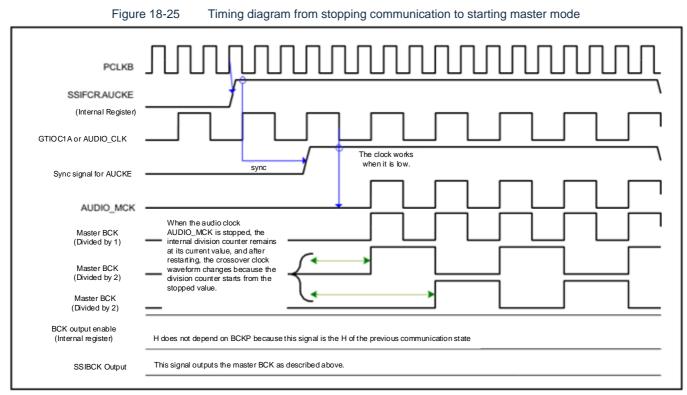

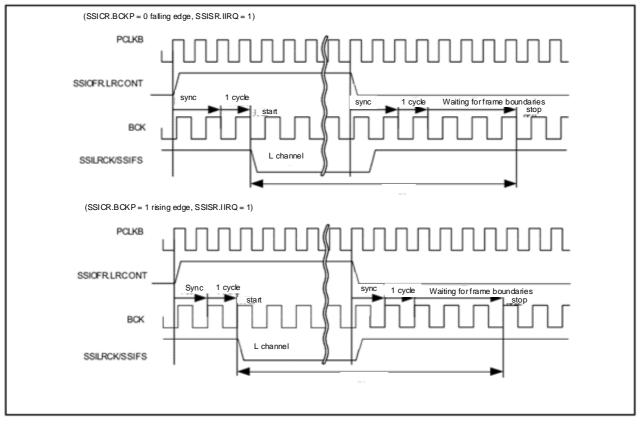

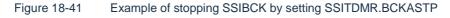

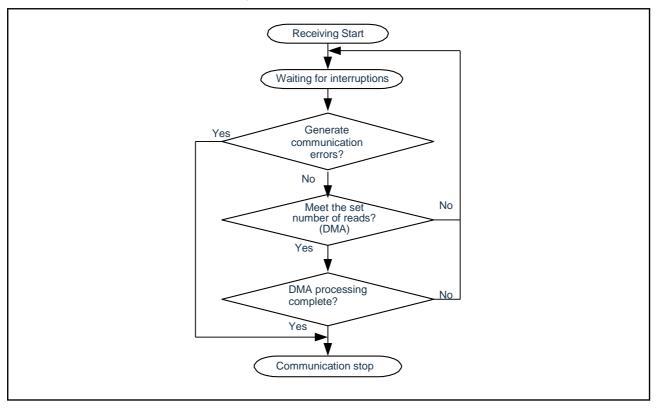

| 18.7.7       Restoring communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18.7.5  | Stopping communication                                                                           | 647 |

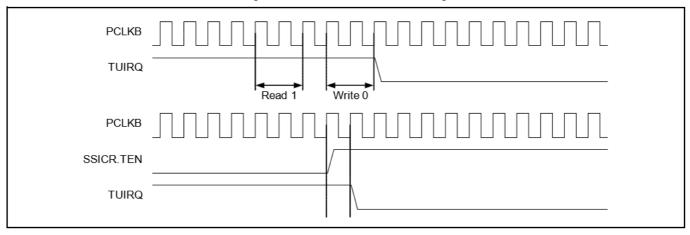

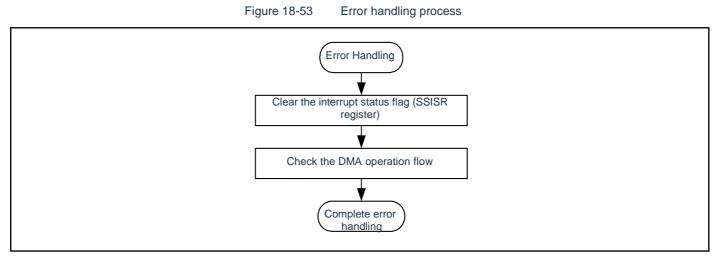

| 18.8       Interrupt       651         18.8.1       SSIE0_SSIF interrupt       651         18.8.2       SSIE0_SSITXI interrupt (full duplex communication)       652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.9.1       Soft reset process       653         18.02       Cautions       655         18.102       Cautions for slave mode communication       655         18.10.2       Cautions for master mode communication       655         18.10.2       Cautions for communication process       656         18.10.3       Cautions for communication process       655         18.10.4       Write access restrictions       657         Chapter 19       Serial Interface IICA       659         19.1       Function of serial interface IICA       659         19.1.2       I²C bus mode (multi-master capable)       655         19.2.3       Viruture of serial interface IICA       662         19.2.4       IICA shift register n (IICAn)       663         19.2.5       Structure of serial interface IICA       662         19.2.4       URA       Make-up mode       655         19.2.5 <td< td=""><td>18.7.6</td><td>Error handling</td><td>648</td></td<>                          | 18.7.6  | Error handling                                                                                   | 648 |

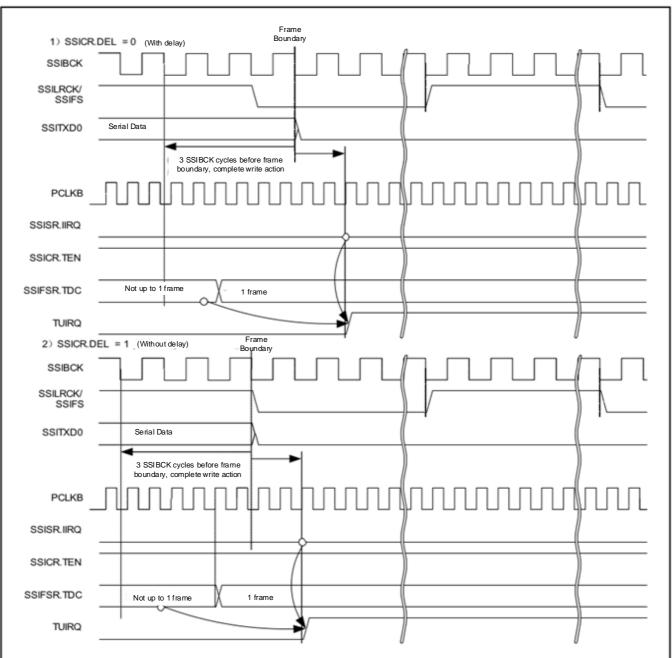

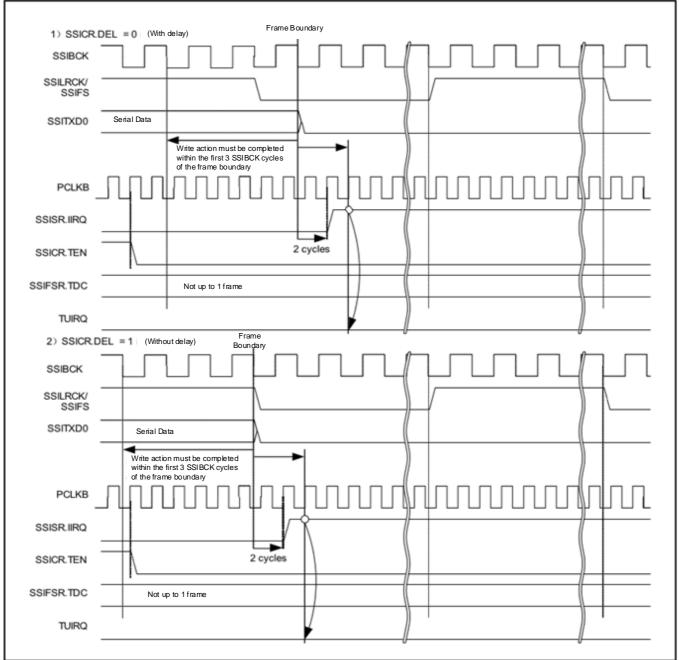

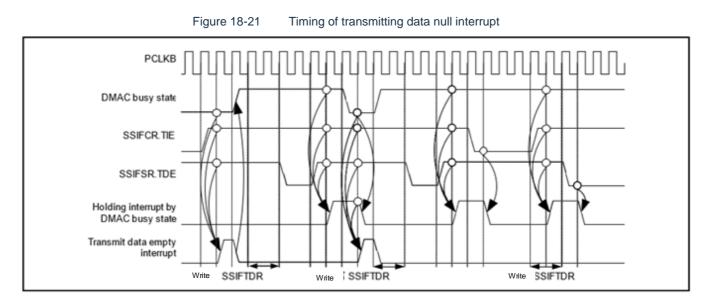

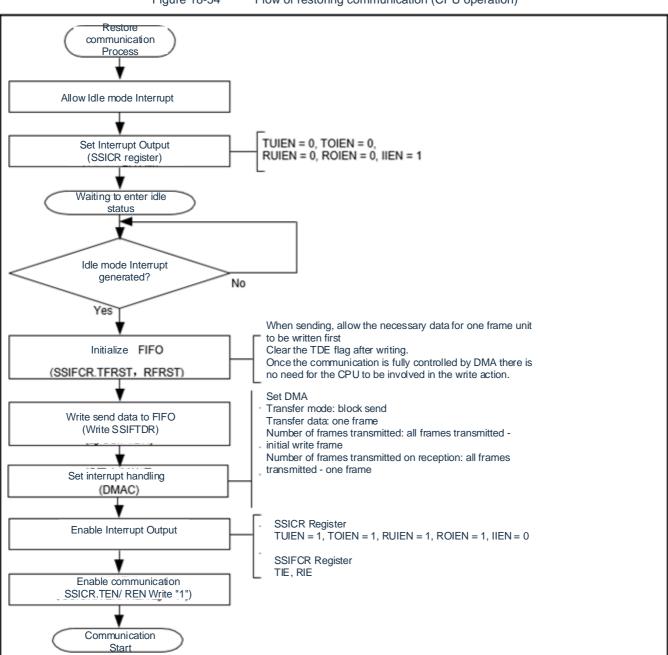

| 18.8.1       SSIE0_SSIF interrupt.       .651         18.8.2       SSIE0_SSITXI interrupt (full duplex communication)       .652         18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       .652         18.9       Soft reset       .653         18.9.1       Soft reset process       .653         18.00Cautions       .655                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18.7.7  | Restoring communication                                                                          | 650 |

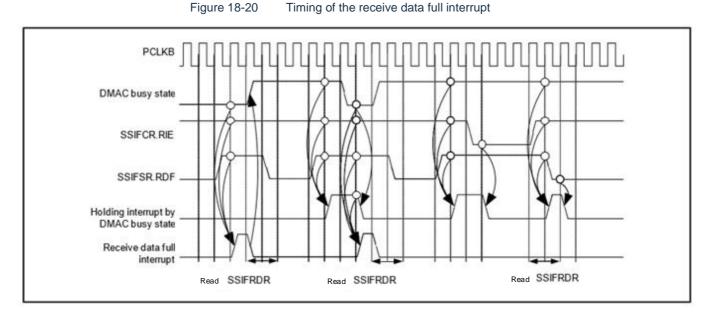

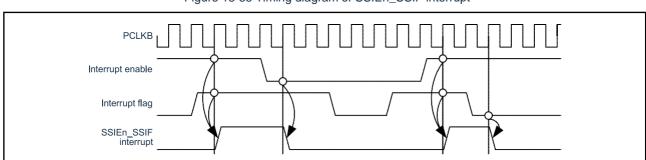

| 18.8.2       SSIE0_SSITXI interrupt (full duplex communication)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18.8 In | terrupt                                                                                          | 651 |

| 18.8.3       SSIE0_SSIRXI interrupt (full duplex communication)       652         18.9       Soft reset       653         18.9.1       Soft reset process       653         18.10Cautions       655       655         18.10.1       Cautions for slave mode communication       655         18.10.2       Cautions for master mode communication       655         18.10.3       Cautions for communication process       656         18.10.4       Write access restrictions       657         Chapter 19       Serial Interface IICA       659         19.1       Function of serial interface IICA       659         19.1.1       Idle mode       659         19.1.2       I <sup>2</sup> C bus mode (multi-master capable)       659         19.1.3       Wake-up mode       659         19.2.4       IICA shift register n (IICAn)       663         19.2.2       Slave address register n (SVAn)       664         19.2.3       So latch       664         19.2.4       Wake-up control circuit       664         19.2.5       Serial clock counter       664         19.2.6       Interrupt request signal generate circuit       664         19.2.6       Interupt request signal generate circuit       664                                                                             | 18.8.1  | SSIE0_SSIF interrupt                                                                             | 651 |

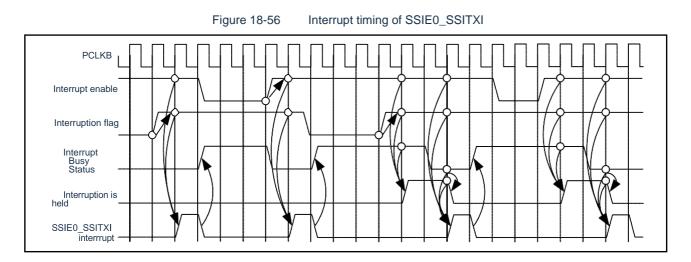

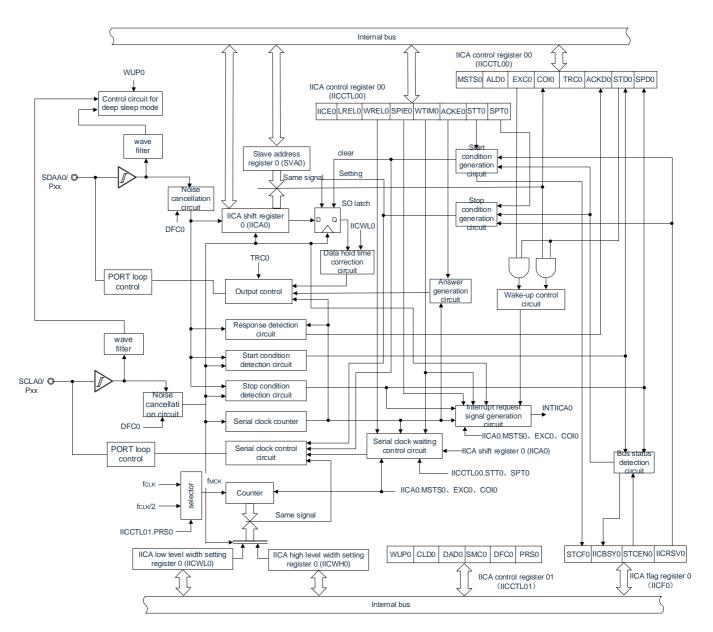

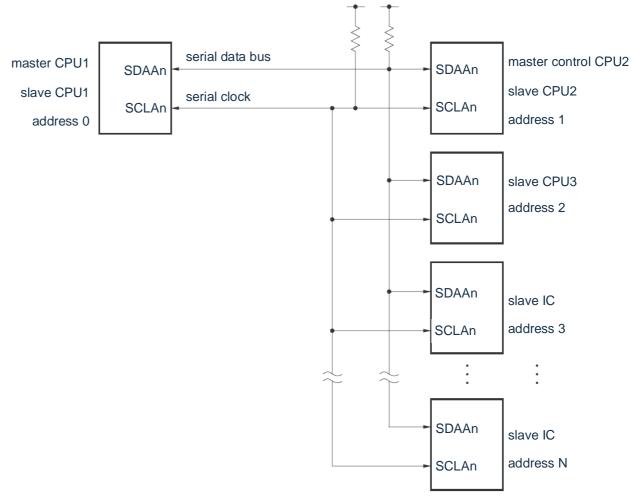

| 18.9 Soft reset       653         18.9.1 Soft reset process       653         18.10Cautions       655         18.10Cautions for slave mode communication       655         18.10.2 Cautions for master mode communication       655         18.10.3 Cautions for communication process       656         18.10.4 Write access restrictions       657         Chapter 19 Serial Interface IICA       659         19.1 Function of serial interface IICA       659         19.1.1 Idle mode       659         19.1.2 I <sup>2</sup> C bus mode (multi-master capable)       659         19.2.3 Structure of serial interface IICA       662         19.2.1 IICA shift register n (IICAn)       663         19.2.2 Slave address register n (SVAn)       664         19.2.3 SO latch       664         19.2.4 Wake-up control circuit       664         19.2.5 Serial clock counter       664         19.2.6 Interrupt request signal generate circuit       664         19.2.7 Serial clock control circuit       664         19.2.8 Serial clock waiting control circuit       664                                                                                                                                                                                                                | 18.8.2  | SSIE0_SSITXI interrupt (full duplex communication)                                               | 652 |

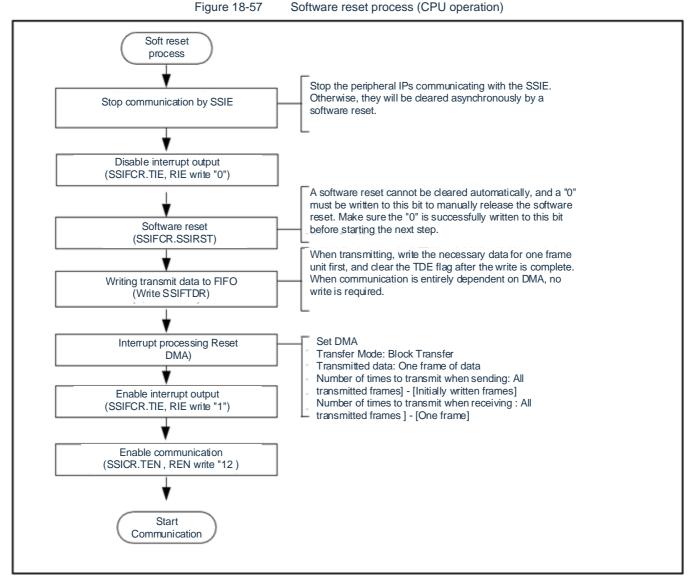

| 18.9.1 Soft reset process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18.8.3  | SSIE0_SSIRXI interrupt (full duplex communication)                                               | 652 |

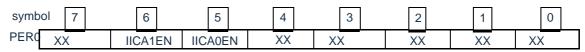

| 18.10Cautions       .655         18.10.1 Cautions for slave mode communication       .655         18.10.2 Cautions for master mode communication       .655         18.10.3 Cautions for communication process       .656         18.10.4 Write access restrictions       .657         Chapter 19 Serial Interface IICA       .659         19.1 Function of serial interface IICA       .659         19.1.2 I <sup>2</sup> C bus mode (multi-master capable)       .659         19.1.3 Wake-up mode       .659         19.2 Structure of serial interface IICA       .662         19.2.1 IICA shift register n (IICAn)       .663         19.2.2 Slave address register n (SVAn)       .664         19.2.3 SO latch       .664         19.2.4 Wake-up control circuit       .664         19.2.5 Serial clock counter.       .664         19.2.6 Interrupt request signal generate circuit       .664         19.2.8 Serial clock waiting control circuit       .664                                                                                                                                                                                                                                                                                                                              | 18.9 S  | oft reset                                                                                        | 653 |

| 18.10.1 Cautions for slave mode communication       .655         18.10.2 Cautions for master mode communication       .655         18.10.3 Cautions for communication process       .656         18.10.4 Write access restrictions       .657         Chapter 19 Serial Interface IICA       .659         19.1 Function of serial interface IICA       .659         19.1.2 I/2C bus mode (multi-master capable)       .659         19.1.3 Wake-up mode       .659         19.2 Structure of serial interface IICA       .662         19.2.1 IICA shift register n (IICAn)       .663         19.2.2 Slave address register n (SVAn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18.9.1  | Soft reset process                                                                               | 653 |